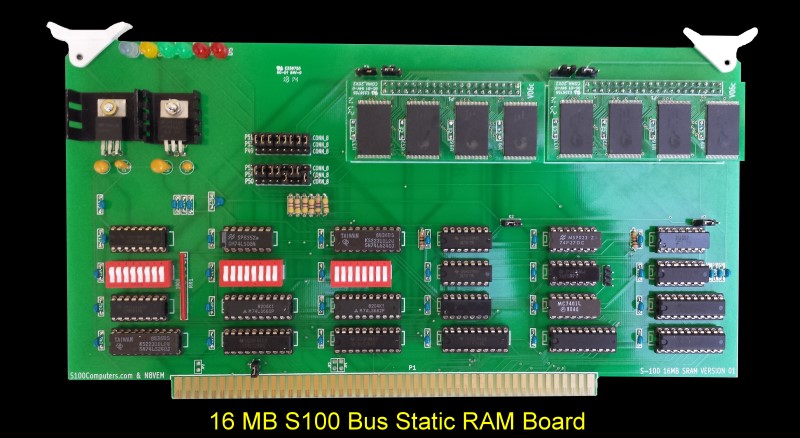

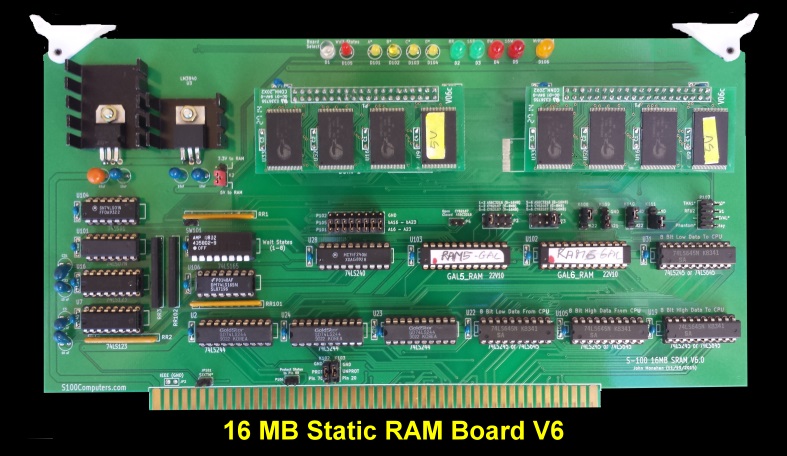

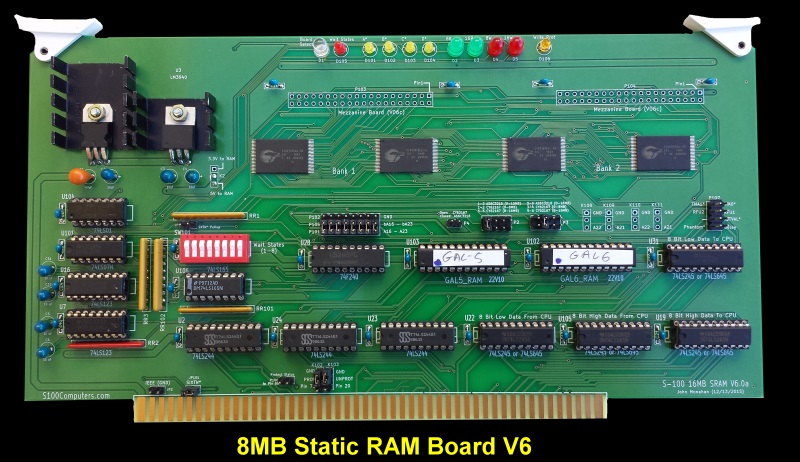

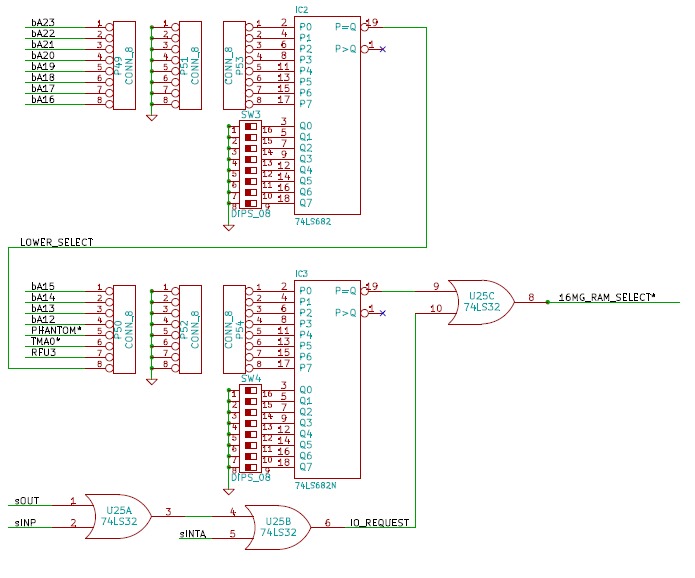

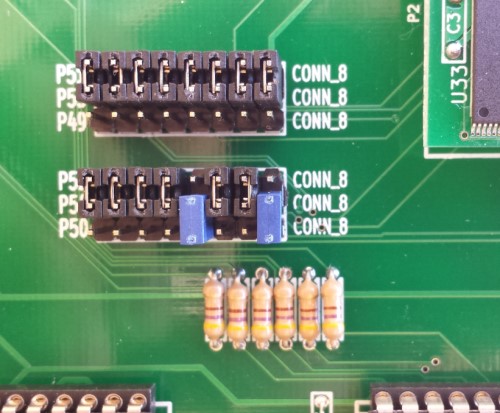

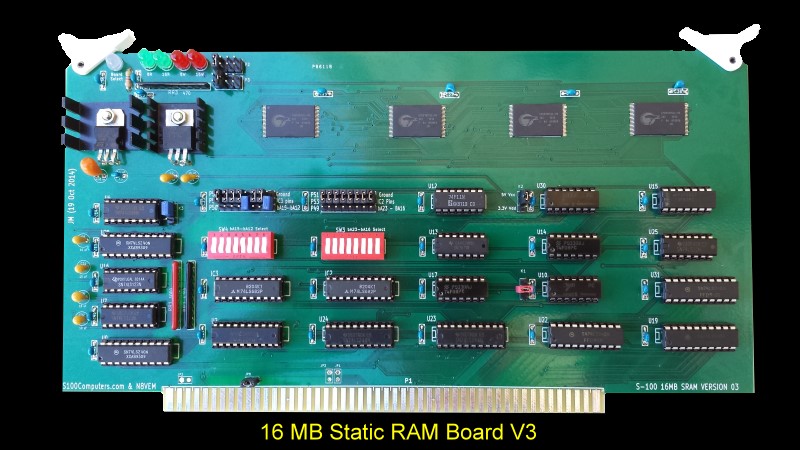

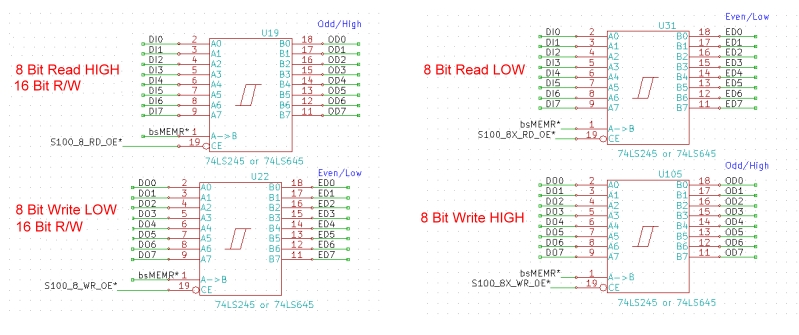

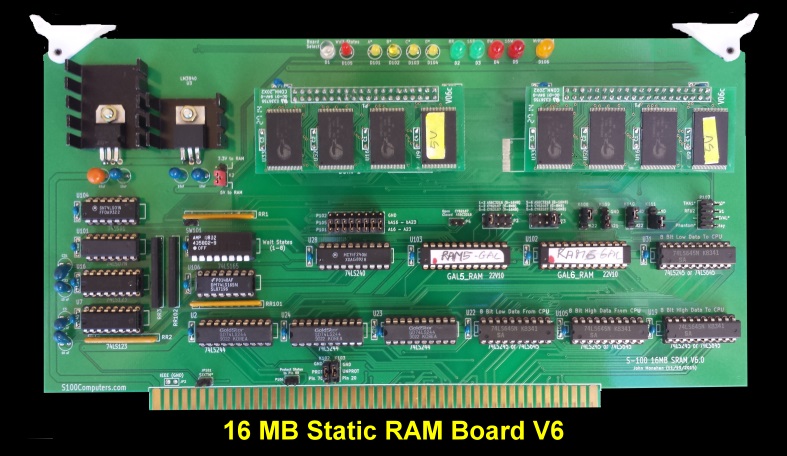

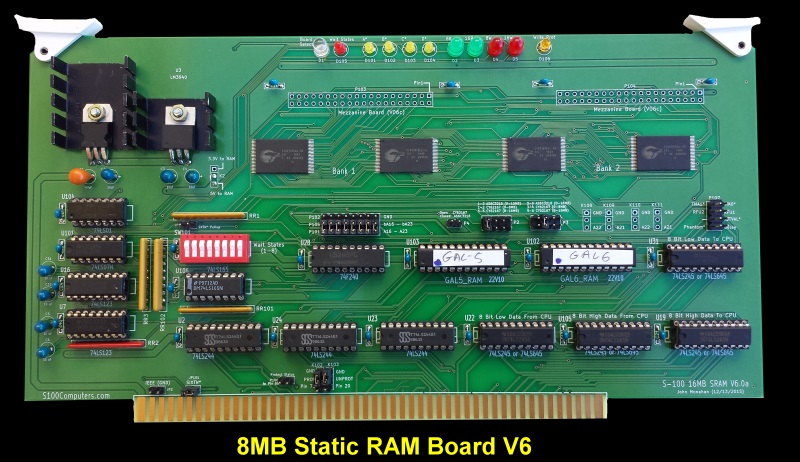

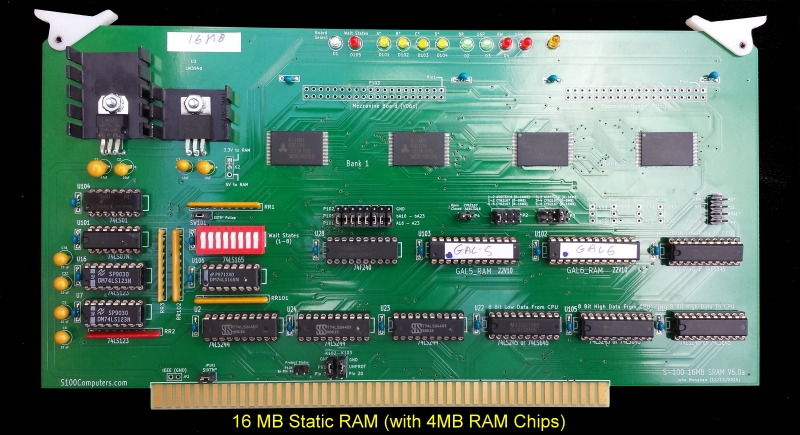

We will now build the board up in functional steps. Avoid the temptation of adding everything at once and popping it into your S-100 box. Step by step is faster in the end -- trust me. However unlike our other CPU boards you have a chicken/egg situation here because you need a functional RAM board to test the board itself. The easiest approach is to start with an old S100 RAM board (of almost any kind) that is working. Boot your system up with that board. Insert all the IC's in our 16MG RAM except U19, U31 and U32. Also bend out pin 4 of U10 (RDY). Do not insert the two RAM mezzanine boards yet. Set all the dip switch positions of SW 2 to open (no wait states). Set all switch positions of SW3 and SW4 to closed

except SW4 position 5 (Phantom*). Boot up your system and check that the Board Select LED D1 stays on all the time as you display memory 0 to FFFFH. check that pin 19 of U22 and U19 are pulsing low.

Next insert the remaining IC's including the two RAM mezzanine boards. You must remove your old RAM board. Your system should boot up. If you have an 8086 board check the 1MG of RAM with memory moves etc. If you have our 68K board do the same for the total 16MB of RAM. (The same test can be carried out with the 80286 board but you will have to program the monitor to work in protected mode, see

here).

Please note:

In an

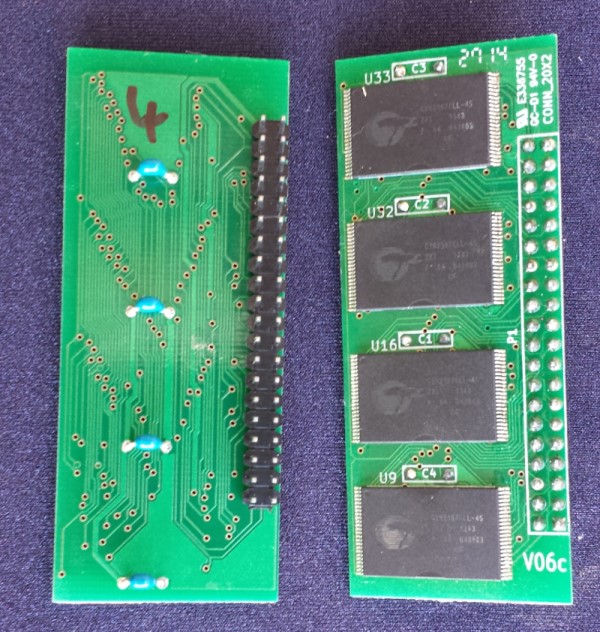

early version of the board there was an error in the jumpers for the mezzanine board. These mezzanine boards were labeled V02.

This mezzanine board has now been replaced by the V06c version. But

just in case you only have the V02 version see below.

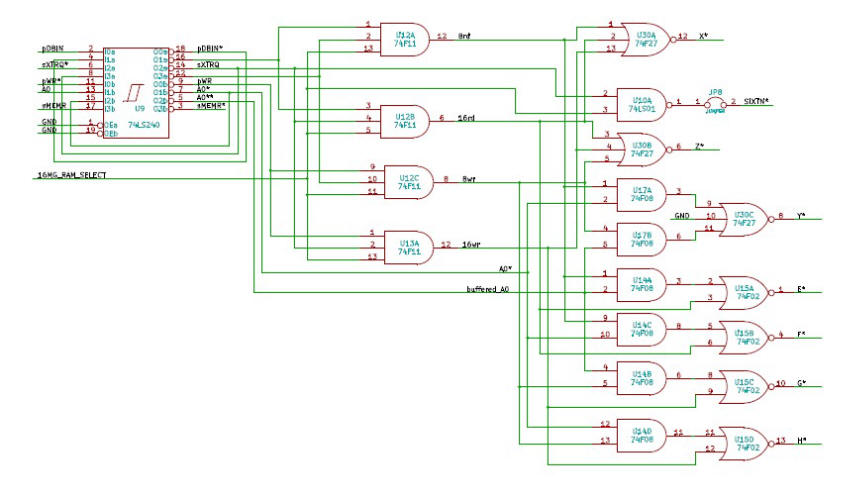

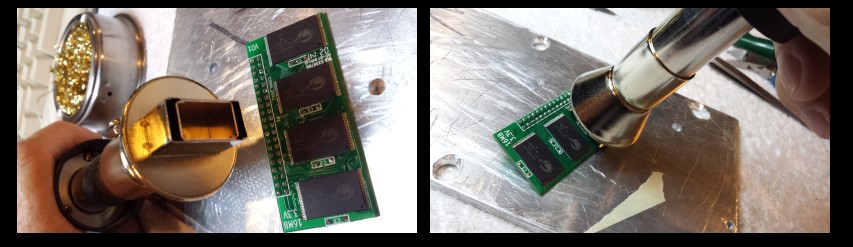

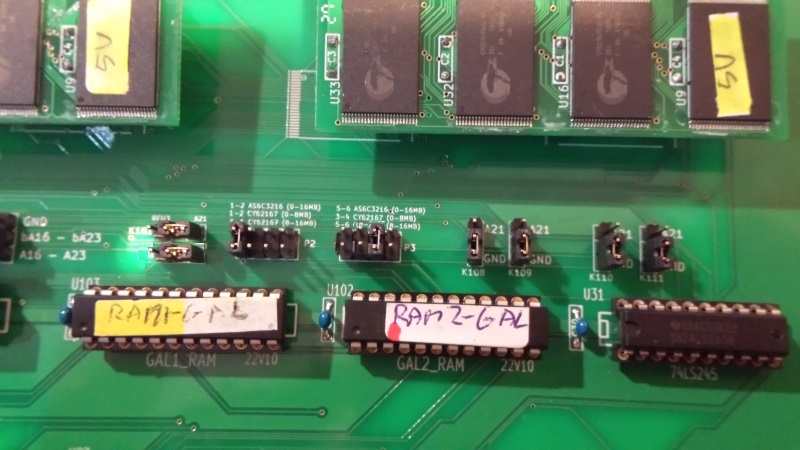

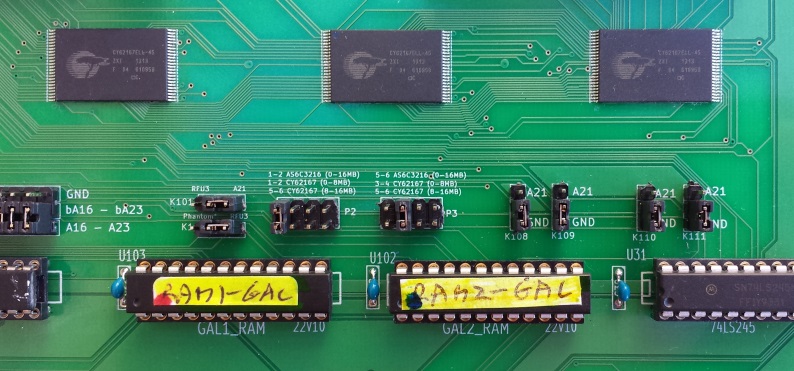

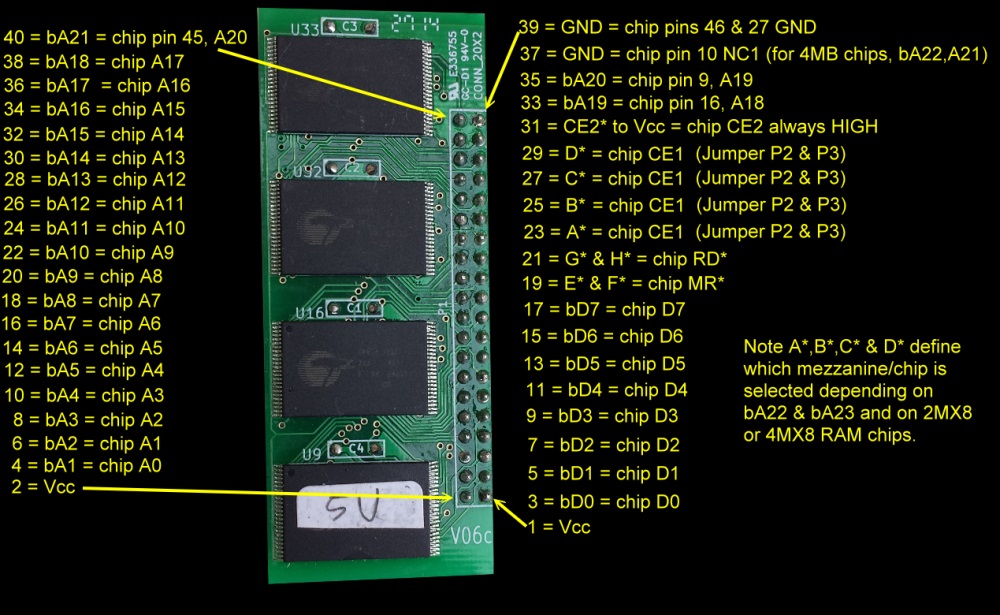

We drew up the schematic for these 16MB mezzanine boards when we were doing the early 32 MG RAM Board a 32 bit data bus board. For this reason the pin names do not really correspond to the actual address lines for this 8/16 bit bus board in the schematics included below. Note this is just a labeling issue, (the RAM chips themselves could not care less), they only examine the 20 address lines coming into the chip. However pin 17 of the RAM chip on the V02 mezzanine boards should be connected to address line bA20 from the parent board (mezzanine pin 37). It is not. This is easily corrected by jumpering pin 35 on the mezzanine board to its pin 37. See picture below. Jumpers K3 and K6 should not be connected to anything, jumpers K4 & K7 should be connected 2-3

(A21). This is not an issue for the V06c mezzanine boards.

David

Fry has done an excellent write-up about this error and the corrections/options available for using either this above CY62167DV30 static RAM chips or the Alliance AS6C3216 static RAM chips. He has gone on to explain how one can in fact use the newer AS6C3216 (4M X 8bit) static RAM chips using only two chips per mezzanine board. Please see here. Thanks David.

A corrected mezzanine board was

later made and it is labeled V06c. The chips I am using are the Cypress CY62167ELL-45ZXI 2MX8 Static RAM chips. I obtained mine from Arrow Electronics, RENO, NV. These are actually 5V chips but they also seem to run fine at 3.3V.

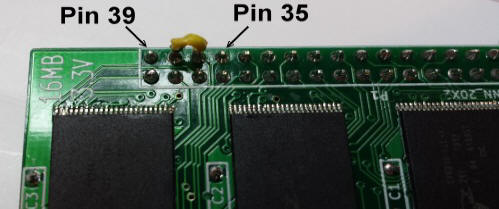

For these chips with 16MB of RAM the jumpers are:-

K4 & K7 2-3 (A21)

K3 & K6 1-2 (Ground)

K2 & K5 2-3 (Vcc)

JP8 Connected

K1 Unconnected

Here is a picture of the address line jumpers:-

So far I have just tested this board with 8 bit read and writes on our Z80 and 6502 boards. I have also tested it with the Cromemco ZPU board and Intersystem's II Z80 board. For 16 bit systems you will need a 16 bit CPU. I have tested the board our own IEEE-696 compatible 8088, 8086 & 80286 boards. It appears to ran it fine with CPM86+ and MSDOS. The board also works fine with the 68000 CPU Board and an 80386 CPU S-100 board. With the fast RAM access of these chips on this board no wait states are required.

Bugs.

The only bug noted so far (apart from the above V02 mezzanine problem), is the

RD/WR LEDs do not light up sufficiently. The pulses are too short. The next version of the board

will use a 74LS123 will be used to stretch the pulses (see below).