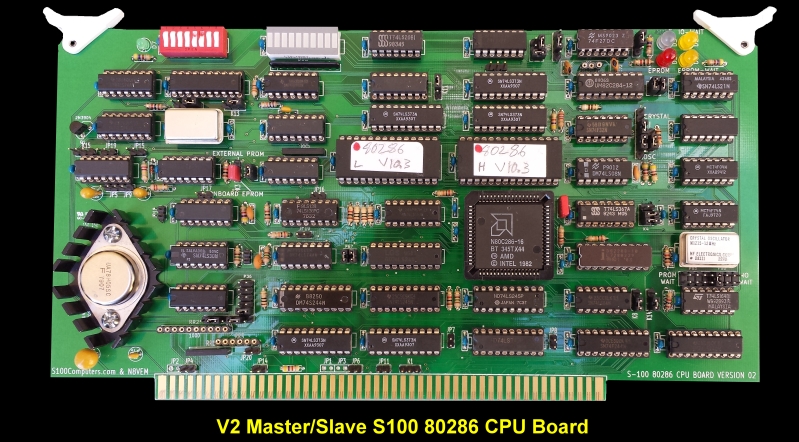

| Jumper | Function |

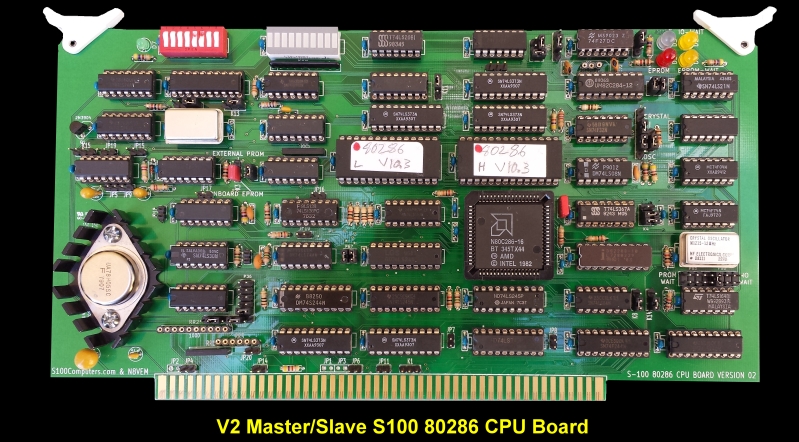

| JP4,JP5,JP6 | Used only if the board is to act as a bus master. Generates Power On reset etc. (Normally open) |

| JP12 | Use only if no other board on the bus pulls up the S-100 HOLD signal (Normally open) |

| JP11 | Use only if no other board on the bus pulls up the S-100 HLDA signal (Normally open) |

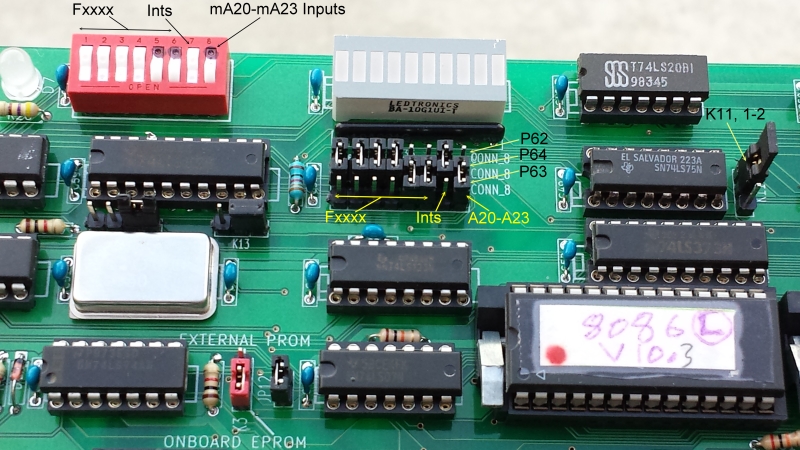

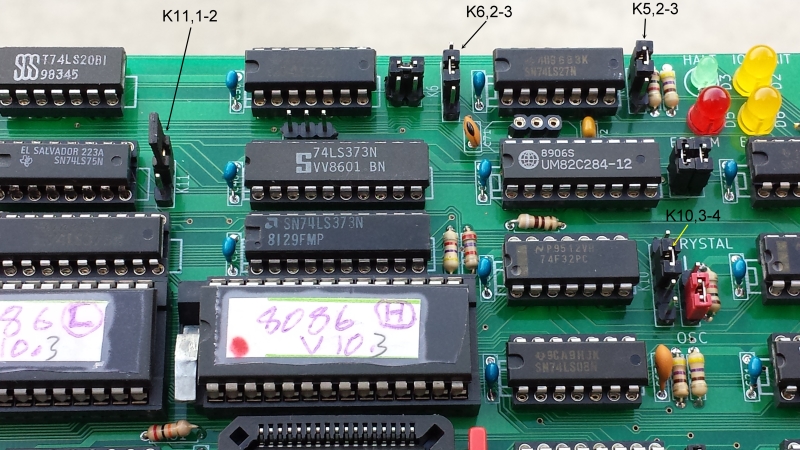

| K11 | This forces the 80286 reset address FFFFF0 to 0FFFF0 so the 8086 and 80286 external ROMS can be used in the same bus. Normally 1-2. |

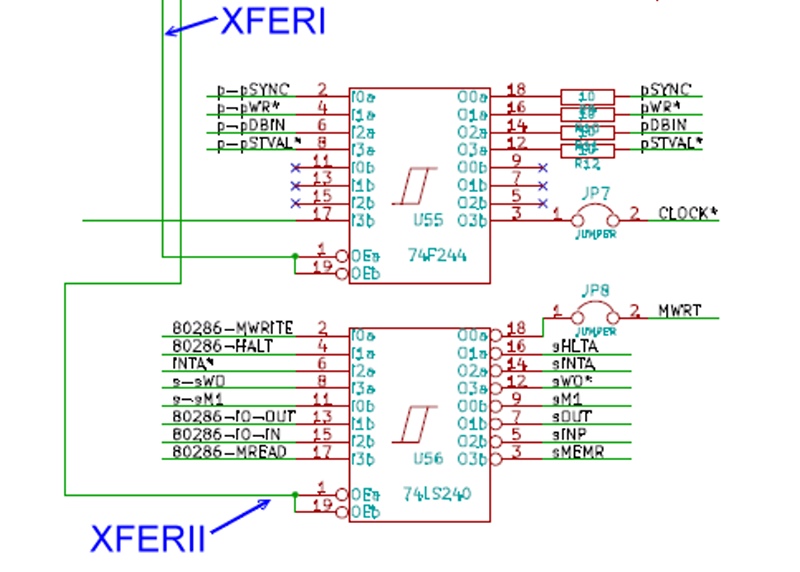

| JP7 | Use only if no other board generates the S-100 2MHz clock signal when the 80286 is active (Closed in my system) |

| JP8 | Use only if no other board generates the S-100 MWRT signal when the 80286 is active (Closed in my system) |

| P65 | Sets number of wait states for onboard EEPROM (0-4). (Open, I use

1 wait state with 28C256 EEPROMS at 12MHz) |

| P66 | Sets number of wait states for bus I/O and INTA cycles (0-4). I use

1 wait state in my system at 12MHz.

(Slow boards generate their own wait states) |

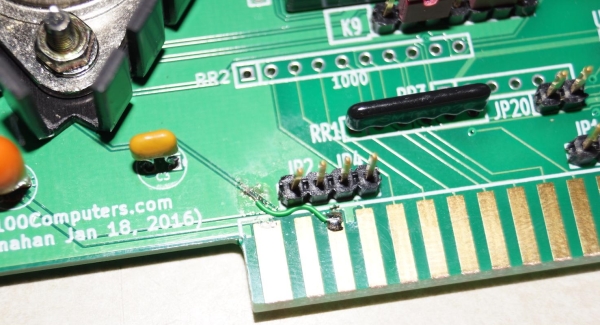

| P57 | Set to slave mode, so 5-6 and 4-2 |

| P36 | Determines what S100 TMA line activates this board. (Normally TMA0*

from SMB, so P26 3-4. For onboard activation use 1-2

& 3-4) |

| K8 | Normally 1-2. MWTC* from 82288. Position 2-3 does not seem to work with some older S100 static RAM boards |

| K14 | Normally 1-2. MRDC* from 82288. Position 2-3 does not seem to work with some older S100 static RAM boards |

| P13, P14 | Use only if no other board on the bus pulls up these signals (Open in my system) |

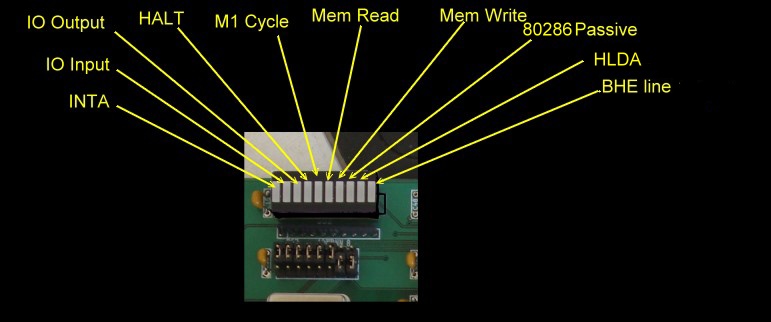

| K1 | Brings the 80286 BHE signal to the bus for experimental purposes (Normally open) |

|

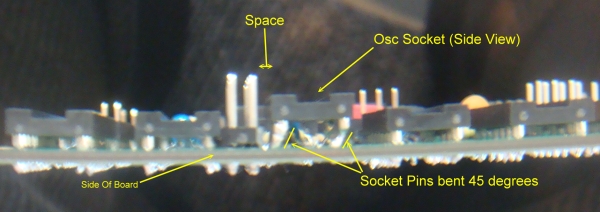

K2 | 1-2, Oscillator supplies CPU clock (4-12MHz). 2-3 Onboard crystal supplies clock (4-12 MHz) (Normally 1-2) |

| K3 | Normally 1-2. If set 2-3 the onboard EEPROM circuit is invisible to the 80286.

Use the latter if using ROMS for example on the MSDOS support board. |

| K5, K6 | These pins must be carefully selected for different EEPROM and EPROM types (For 28C256's, K5 2-3, K6 2-3) |

| K4 | Determines when the 80286 LEDs are enabled. (Normally

5-6 & 3-4) |

| P67 |

Normally 1-2 and 3-4. This selects the port to activate the 80286

board on the bus, port EDH |

| SW3 | This selects where the onboard EEPROMS will reside in the CPU's 1MG address space

Normally 28C256 ROMs will be at FF000H, so SW3 will be

open, open, open, open, closed, closed, open, open |

| RR2, RR3 | Insert a 1K resistor network in these positions IF no other board on the bus pulls VI0* - VI7* etc. high. Normally they are not jumpered (they are pulled up by the Z80 master CPU). It is essential multiple boards do not pull them high. |

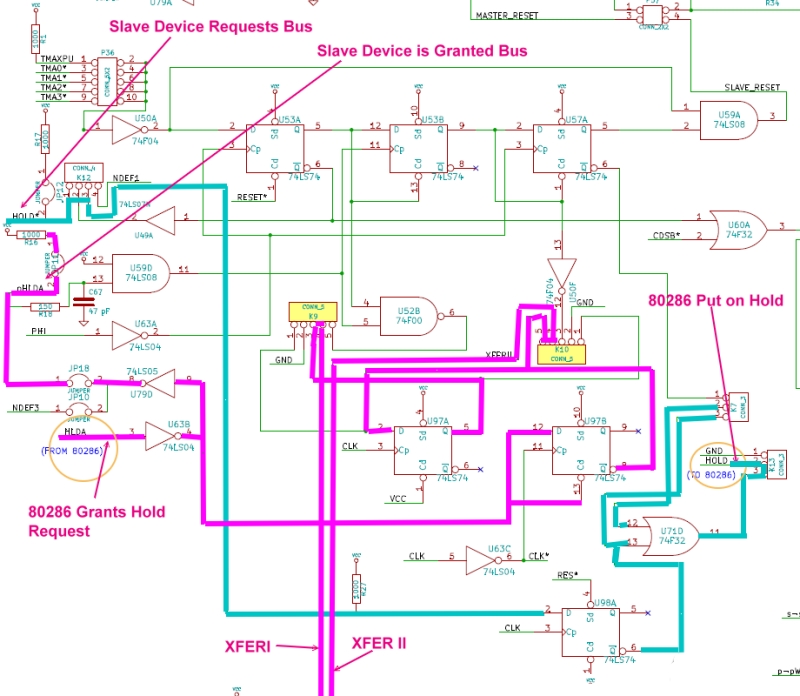

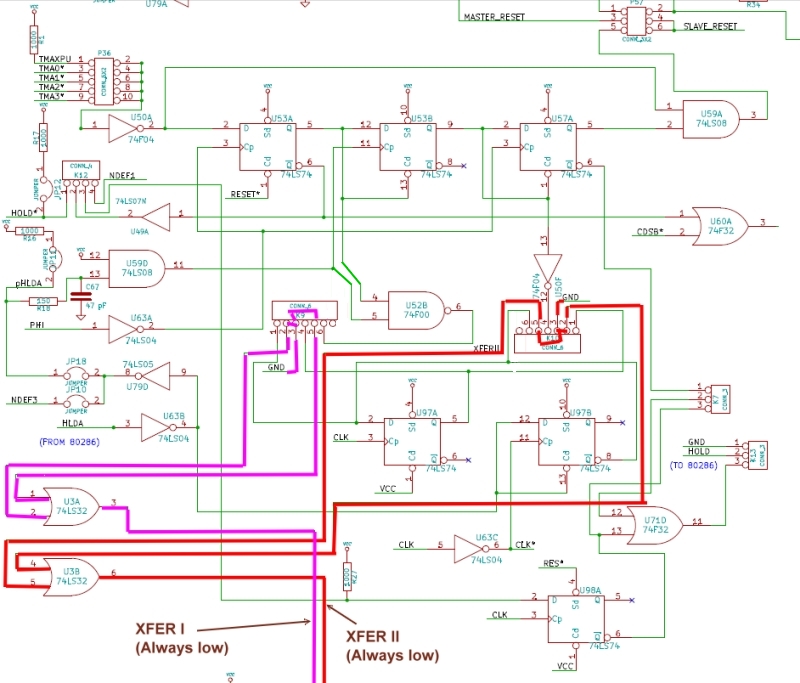

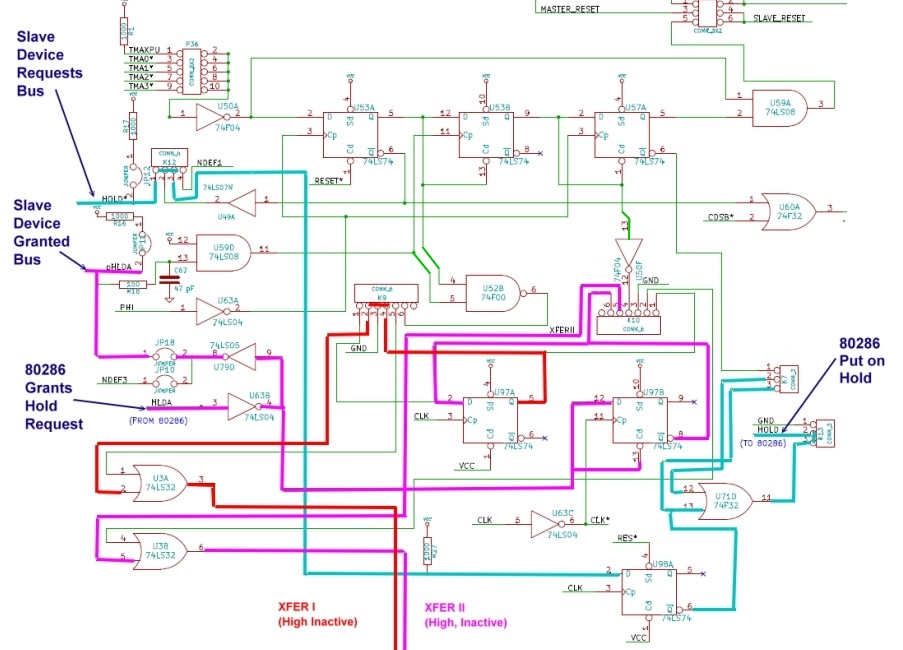

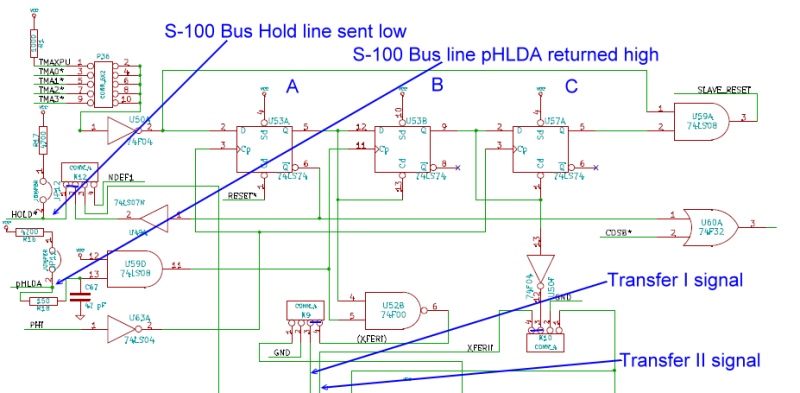

| K9 | Determines when/how the XFER-I process takes place (For Slave mode 2-3 and 5-6) |

| K10 | Determines when/how the XFER-II process takes place (For slave mode

2-3 and 4-5) |

| JP10 & JP18 | Open

in slave mode |

| K12 |

Send HOLD* request back to

master (Z80), so K12 1-2 |

| K7 & K13 | Used to put 80286 in hold state

when high. Here, K7 2-3 and K13, 1-2 |

|

JP1,JP2 & JP3 |

If you S-100 bus is IEEE-696 compatible these jumpers allow extra

ground access to the board. Most S-100 busses don't have this

installed |

JP9,JP16,PP17,

JP19 & JP15 |

These jumpers allow the board to disable the address, data, status

and data lines. Not really relevant here but can be jumpered |

.jpg)