| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

| A simple address management system that provided two 1 Kilobyte segments reloadable anywhere in the first megabyte of the 16 megabytes of the S-100 address apace. Four light-emitting-diodes Indicate the four most-significant address bits. | |

| A Vectored Interrupt Controller that provided sophisticated, high speed interrupt handling with individual masking, fixed or rotating priorities, and optional polled operation. | |

| 2 or 4 MHz processor speed which was on-board pin-jumper selectable. | |

| PROM monitor socket will accept 2708, 2716, 2759, or 2732 EPROM's and a reset jump is provided to the PROM. | |

| The PROM may be addressed at any 1 K boundary in the 64 K address space. | |

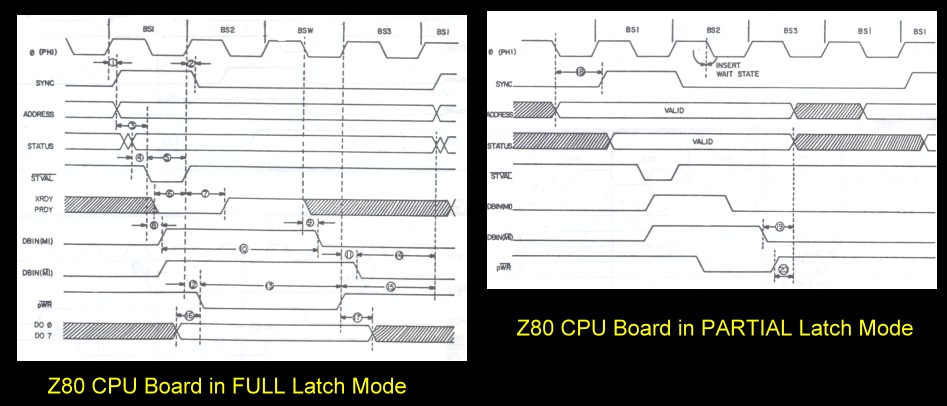

| On-board wait generator optionally adds a single wait state to any Instruction Fetch, Memory Reference, Input/Output Reference, or on-board PROM Reference. | |

| On-board circuit conducts the IEEE specified nested bus transfer for glitch-free DMA operations, and DMA controllers need not duplicate the circuit. | |

| Special engineering features included 2 self-test modes for quick circuit debugging and Address and Status latching to reduce bus noise and improve reliability. |

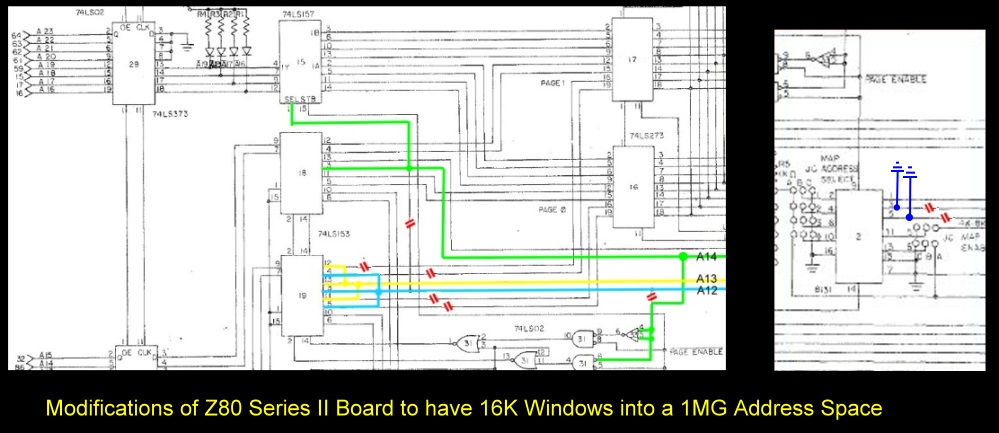

Here are some more examples to explain the translation system

| S100 Address lines | |||||||||||||||||||

| A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| 7 | 6 | 5 | 4 | 3 | 2 | ||||||||||||||

| Port 0D2H | |||||||||||||||||||

Examples:-

Address 0000 0000H + Port D2H = FCH

translates to an address of 000F C000 0000H

Address 0000 0000H + Port D2H = 10H

translates to an address of 0001 0000 0000H

Address 0000 0000H + Port D2H = 14H

translates to an address of 0001 4000 0000H

Address 0000 1000H + Port D2H = 14H

translates to an address of 0001 4000 1000H

Disabling the Onboard PROM of a IA-Z80 Card

The second modification I made to this board was to allow the

disabling of the on-board EPROM under software control. Without this the EPROM

will appear in each 64K segment of memory. In may case at 0F000H-0FFFFH,

1F000H-1FFFFH, 2F000H-2FFFFH.... Particularly useful is the ability to remove the

EPROM from the first 64K of RAM allowing a 64K CPM3 system.

To accomplish this we take advantage of the fact that the above 16K window

mapping frees up bits 0 and 1 of ports D2H and D3H (or whatever address you have

yours jumpered to by Jumper JD). If we cut the board trace of pin 14 of U1

(going to jumper JB of (A-B-C) and connect a wire from pin 14 of U1 to pin 19 of

U17 (data line 0) we can disable the EPROM anytime we output to port D3

with bit 0 equal to 1. So in our example above if we output to D3H 0F9H we will

relocate the RAM window and remove the EPROM addressability from the board. Note

you cannot do this from your monitor in ROM because you will have removed the

next op-code the Z80 would receive.

To test, recompile the Z80 monitor to say 8000H, load it with ZSID, jump

to 8000H and then output to the D3H port.

16 Bit Port Addressing

The current Z80-Series II board outputs all I/O port address on the high

(A8-A15) and low 8 bit (A0-A7) address lines. Most early S-100 Z80 boards did

this to be compatible with the original 8080 CPU which did the same thing. Actually few if any S-100 I/O

boards utilized these high bits. Because all 8 bit CPU's had a maximum of only

256 ports this was never a problem.

With the introduction of 16 bit systems and the I/O port range now extended to

64,000 ports (i.e. 16 bits), it became relevant if you wanted to address ports

greater than 256 to have 16 bit I/O addressability on the bus. The good

news is it is easy to modify the Z80 Series-II CPU board such that the upper I/O

address lines are zero. In other words the I/O address range is 0000H to

00FFH.

To accomplish this cut the board traces of pins 6 & 10 of U19 and pins 6 & 10 of

U20 (a 74LS157 and 74LS153).

Jumper with a wire all 4 chip pins to ground.

You are done. Now anytime you output to an S-100 port with the Z80 the upper

address lines will be zero. This avoids messing up ports that say an 8086 would

address.

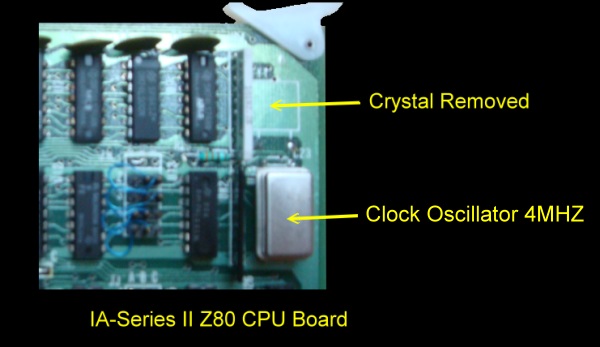

Modifying the Board Clock Signal.

If you find yourself changing the main S-100 clock frequency on

the board a lot as you experiment with other S100 boards (e.g. a slave CPU board)

it is nice to be able to do this quickly. I removed the older clock

circuitry on the board utilizing U14 (a 74LS124) and a 8MHZ crystal) and put in

place a self contained clock oscillator generator "chip". These are very

common now and provide rock solid stable square wave outputs. They have only 4

pins, (ground, +5V and output). To accomplish this..

Remove U14, cut all traces to pins 1,7 and 10. Insert a 14 pin oscillator with

its pin 1 in pin 1 of U14 (pins 8 & 9 are now free). Jumper U14 pins 7 & 8,

and connect U14 pin 9, (8 of oscillator, frequency output) to the trace going to

jumper JG pin B .

Remove the crystal its no longer needed. Remember the clock oscillator in the top section of socket U14 (i.e. a 14 pin

IC in a 16 pin socket, so pins 8 & 9 are free).

You are done. Now to switch frequencies simply plug in the appropriate frequency

generator. I normally start with a 4MHZ system.

The picture below shows

my system.

This page was last modified on 10/25/2013