Notes

No hardware changes have been noted to date.

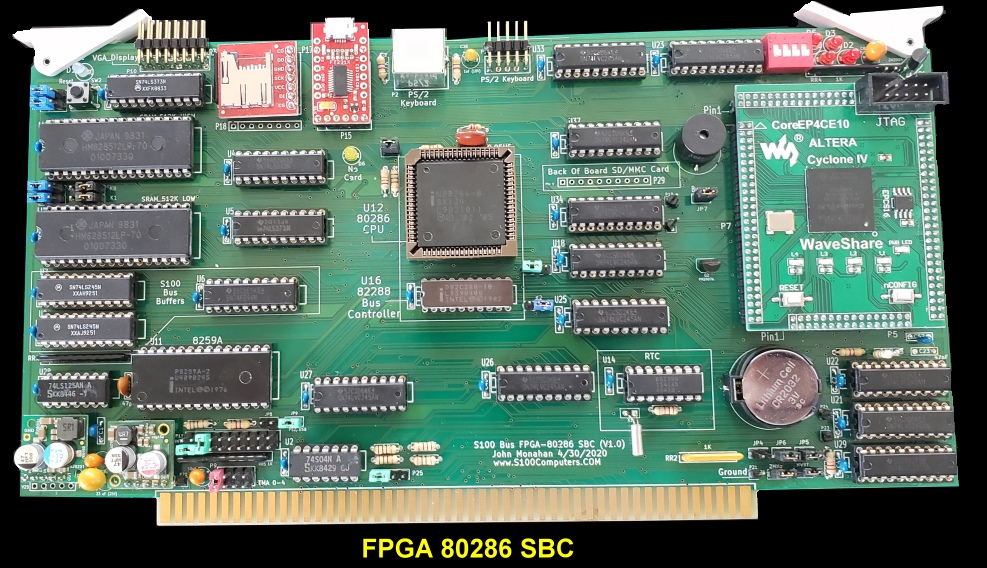

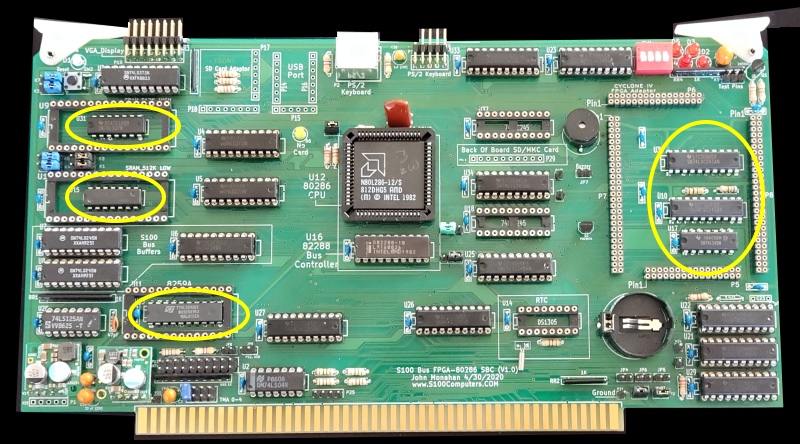

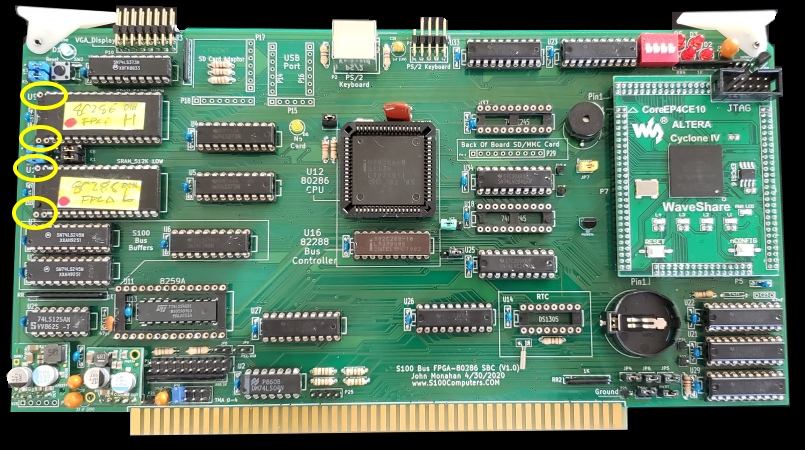

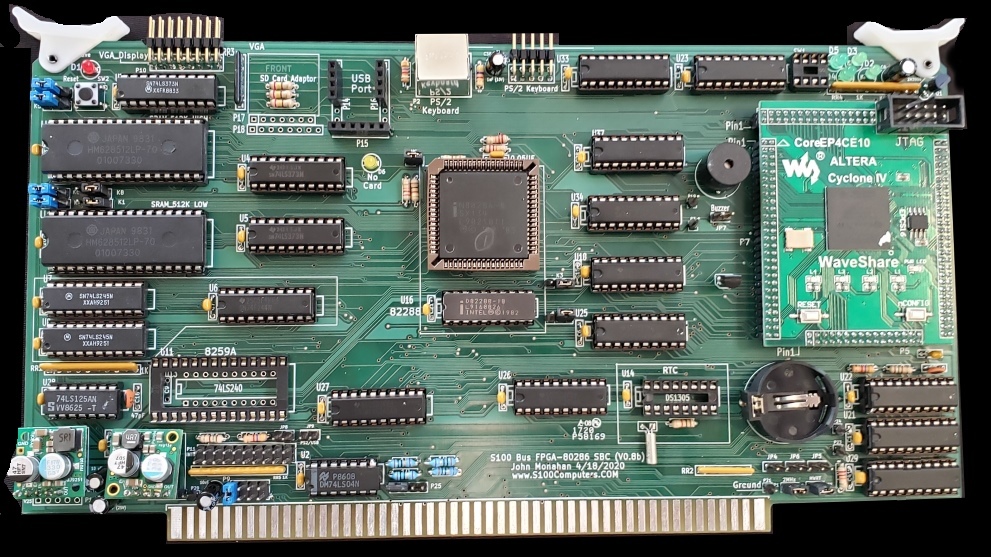

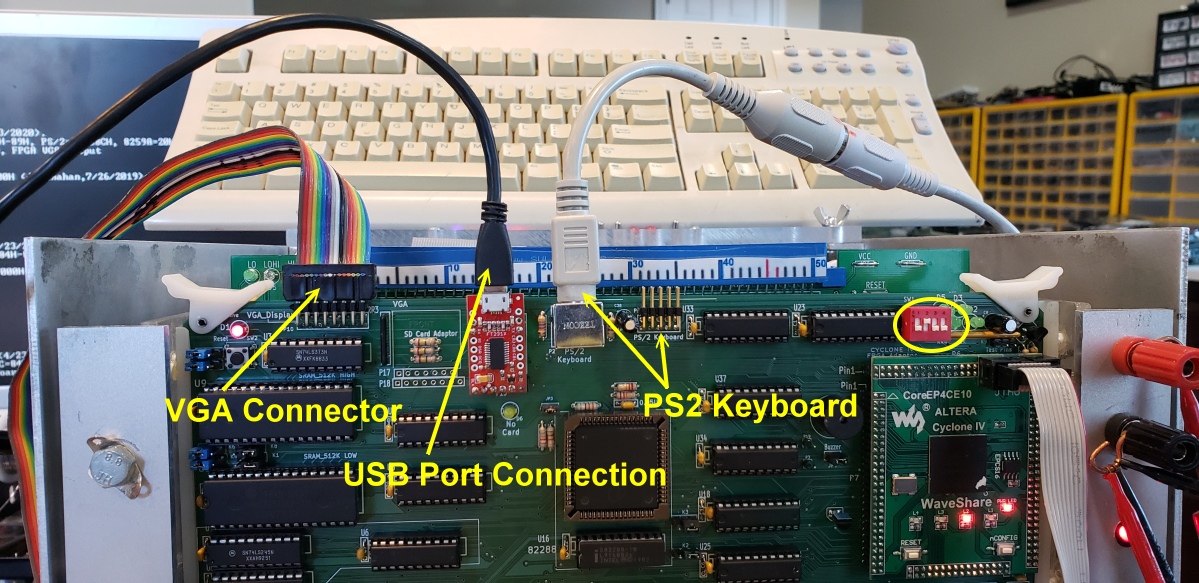

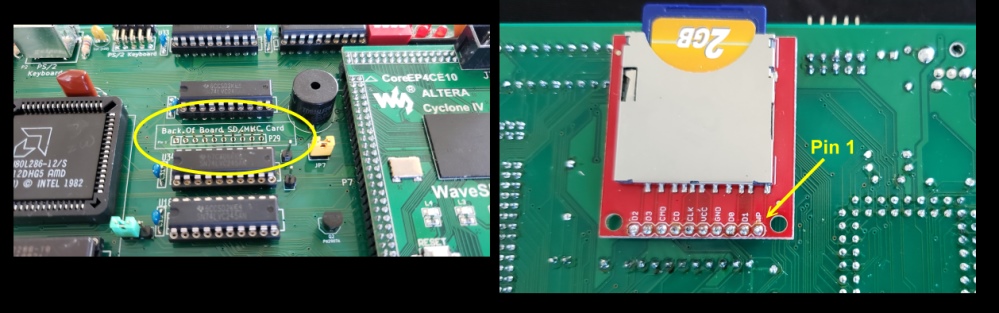

The pictures of the board on this page is actully that of the final

prototype board. The actual "production" board has some very minor changes

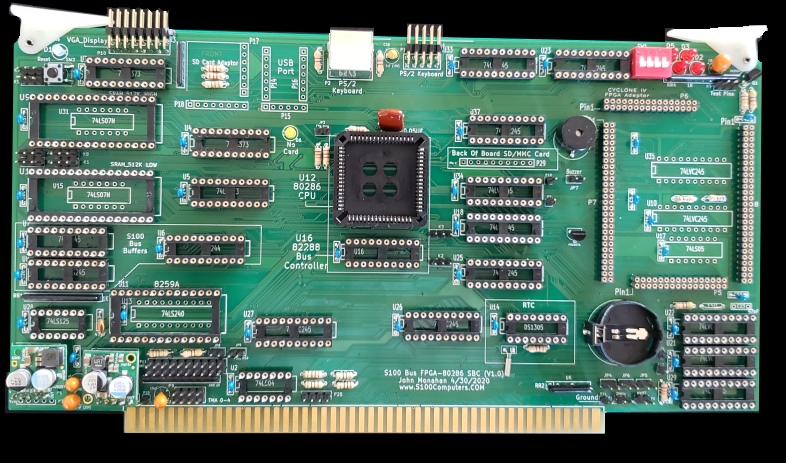

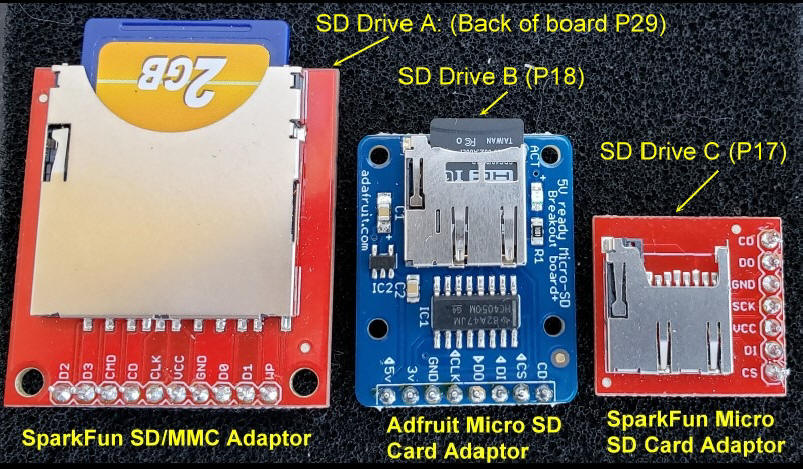

-- mostly silk screen text changes. However I have added pins (P29) to

attach a SparkFun SD/MMC

card adaptor to the back of the board for an extra SD drive (between U37 and

U34). Note pin 1

is on the RHS on the back of the board.

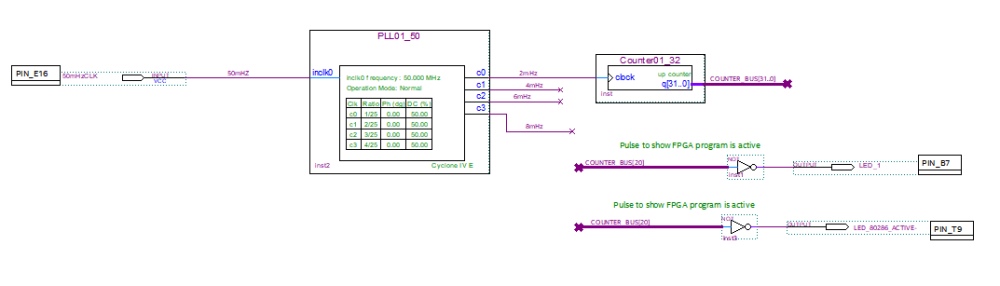

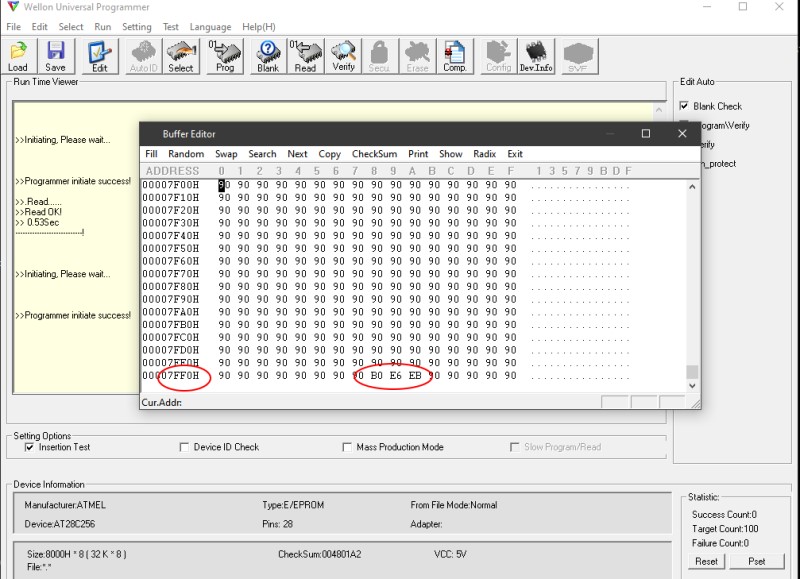

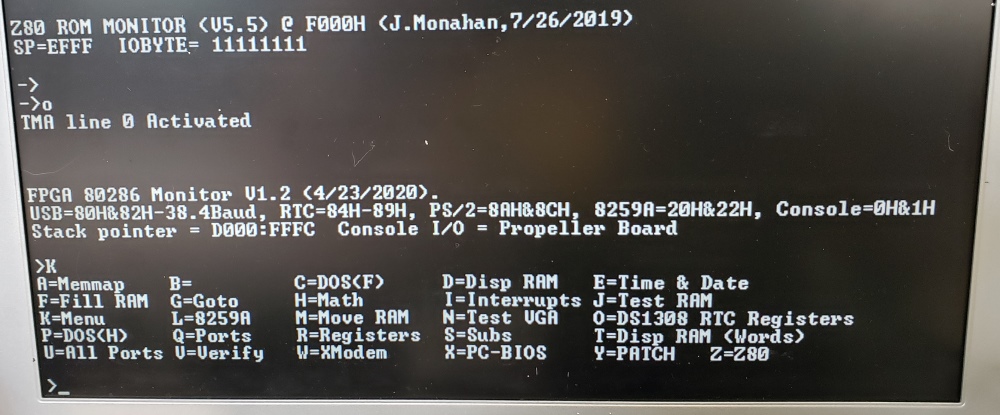

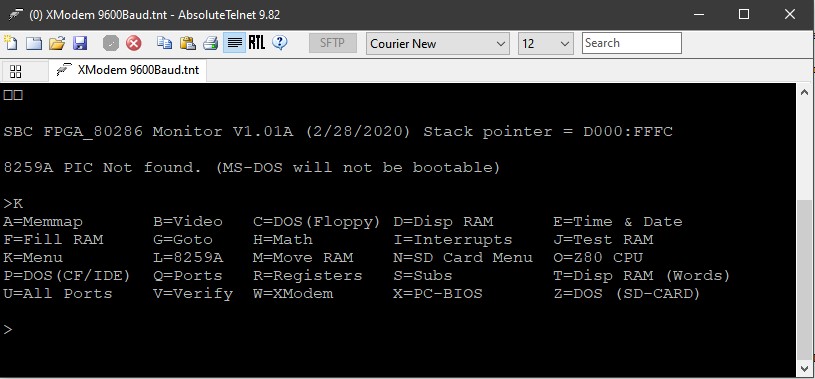

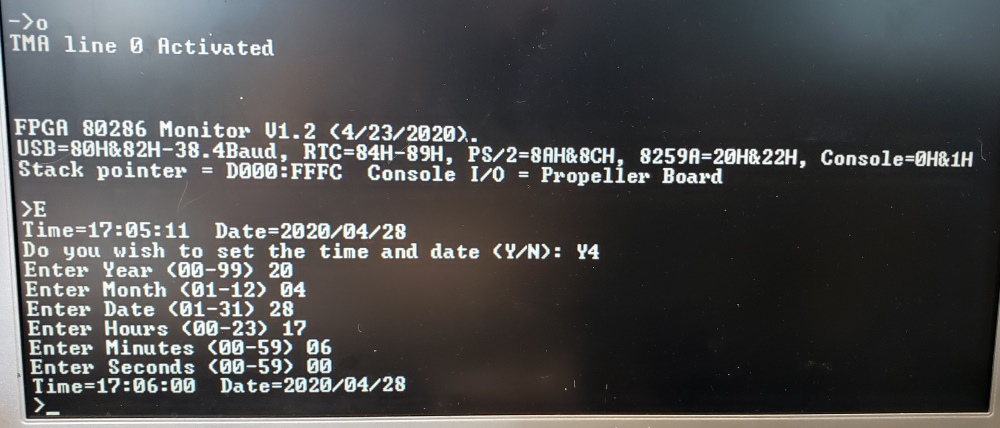

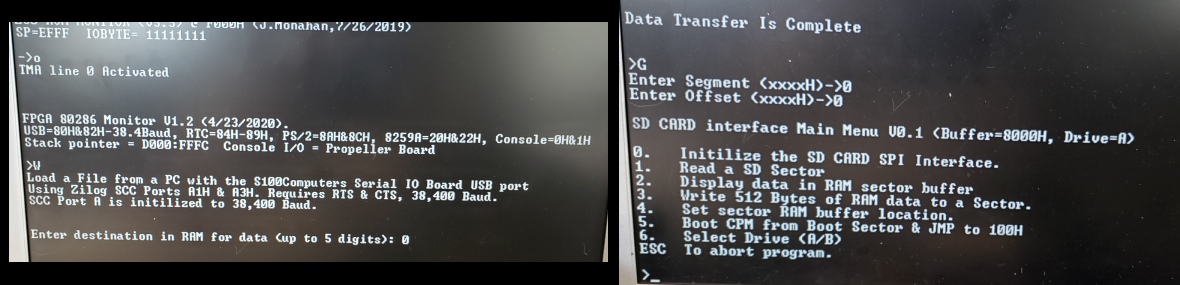

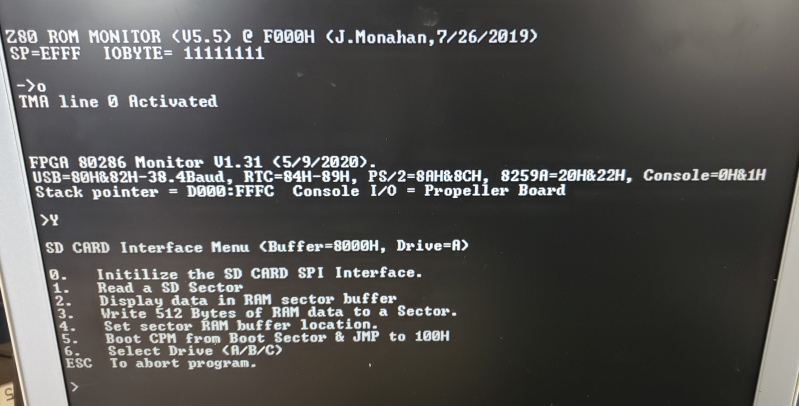

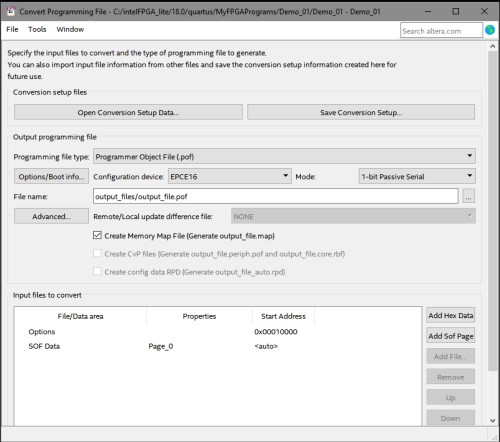

Over time there may be corrections/additions to the 80286 monitor or FPGA

.bdf files. Alway check below and use the most recent versions.

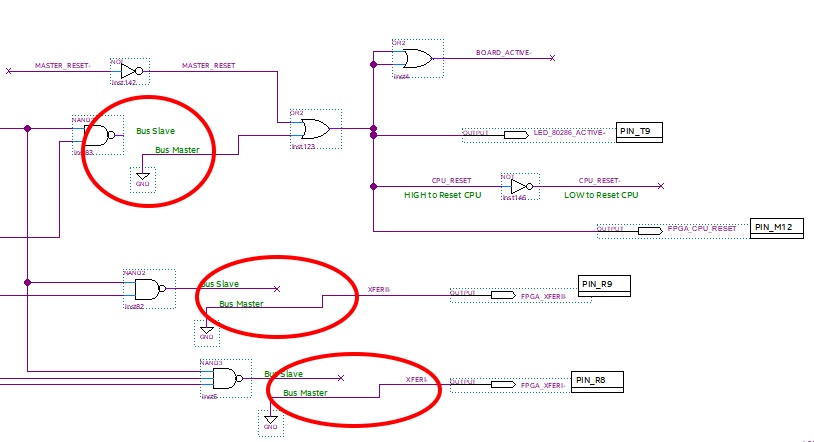

A Self Contained Board

This Board is a completely self contained S100 Bus Master as defined by the

IEEE-696 Specs. It can therefore be run outside the S100 bus if you

simply provide power to it. There are two pins

P20 for ground and

P21 for 8-10V input to do this. Please use the upmost care in

doing this. Make sure the board is sitting on an insulated background

(glass/wood etc.). Of course you will want to configure

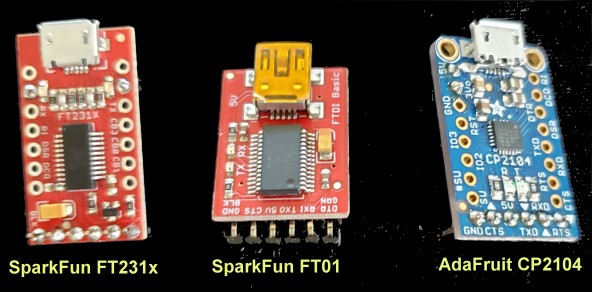

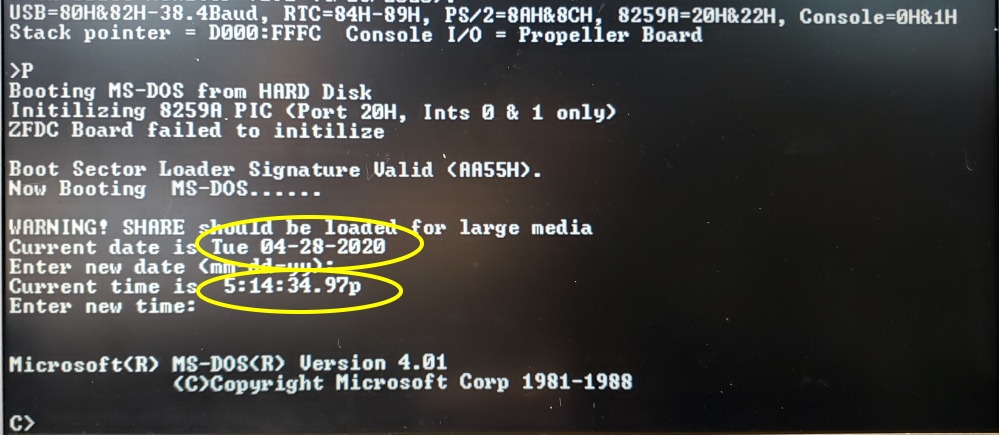

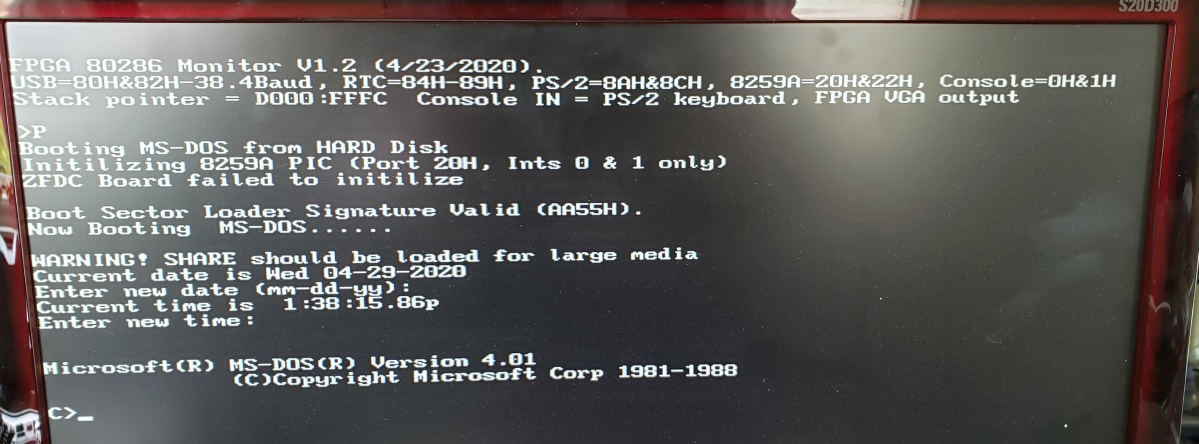

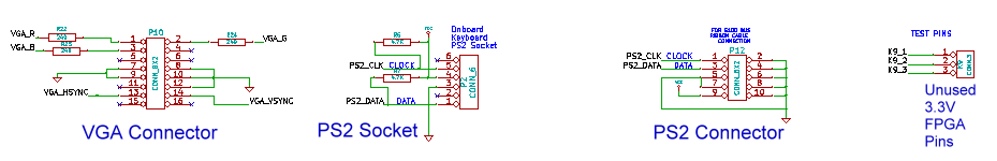

the IOBYTE to the USB port or VGA and PS2

keyboard.