|

| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

||

|

|||

|

Notes

No hardware changes have been noted to date.

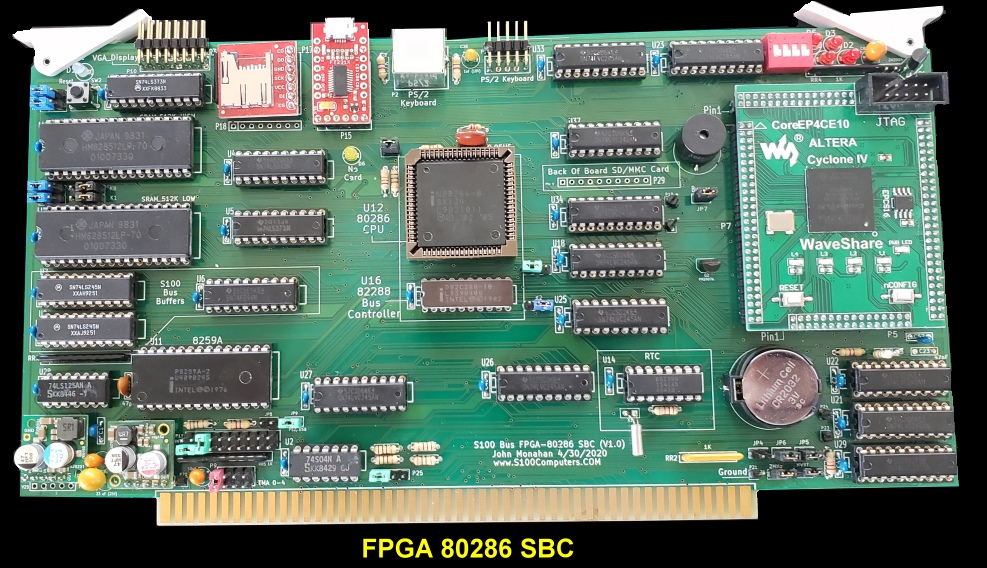

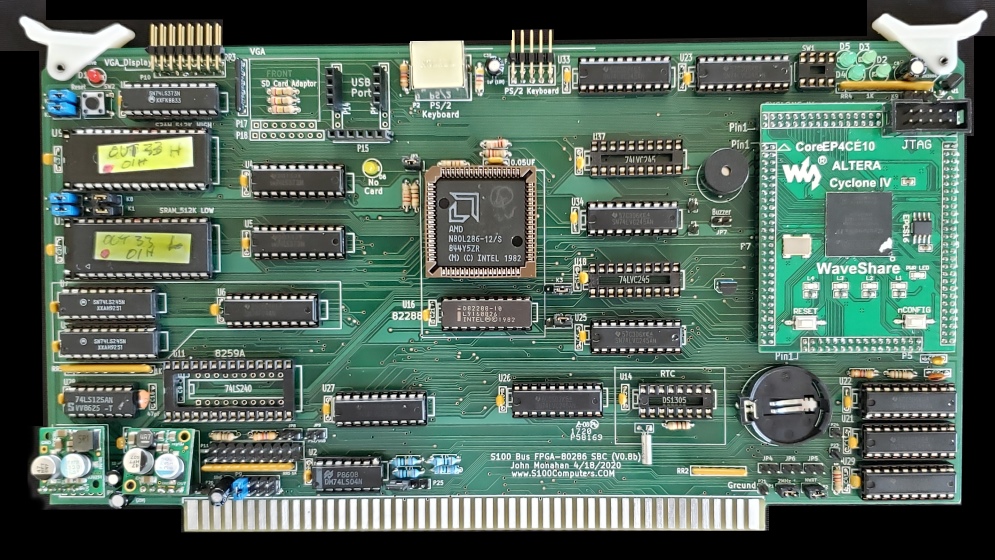

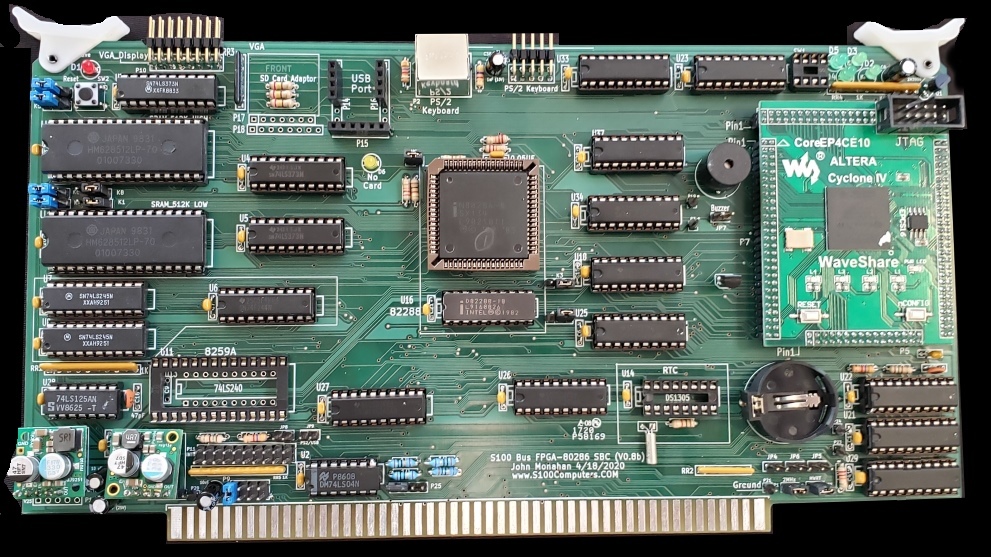

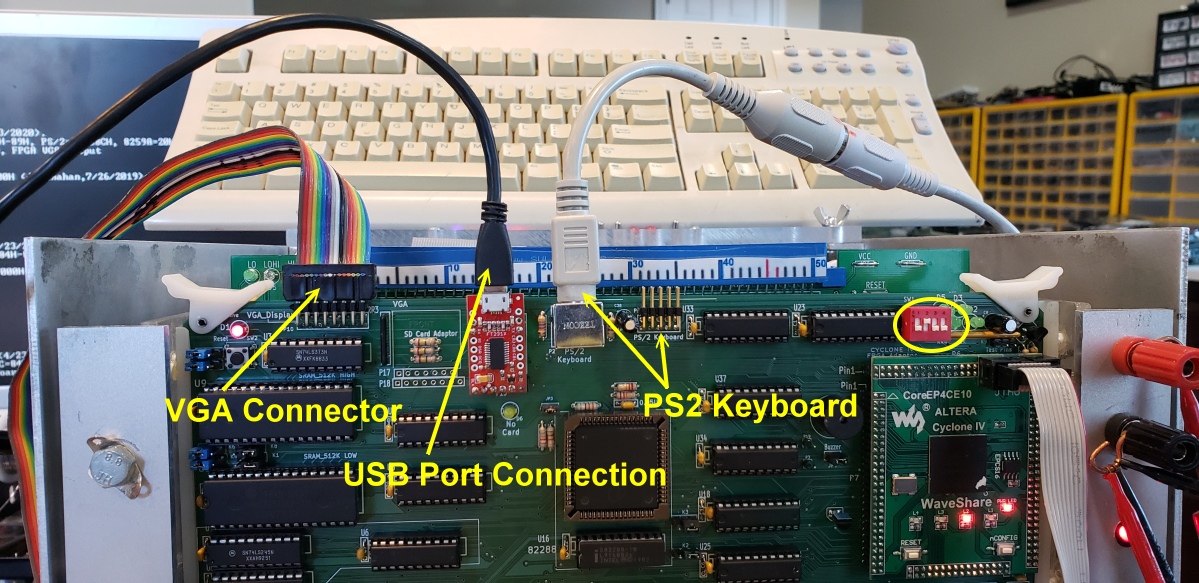

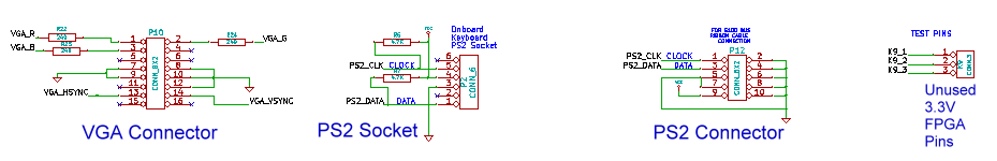

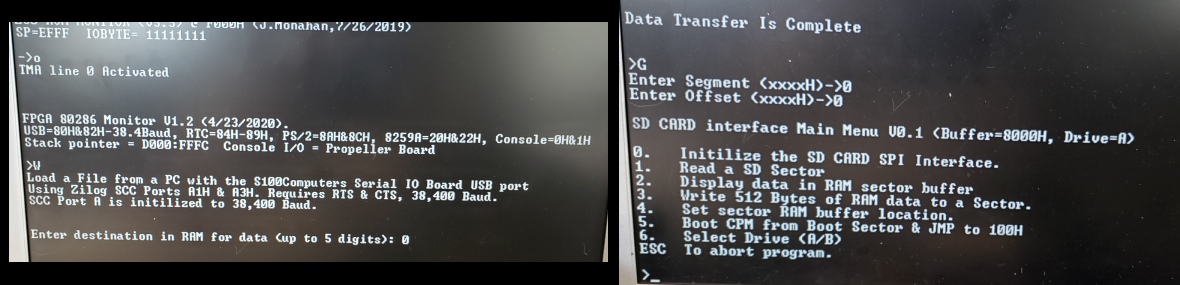

A Self Contained Board

This Board is a completely self contained S100 Bus Master as defined by the IEEE-696 Specs. It can therefore be run outside the S100 bus if you simply provide power to it. There are two pins P20 for ground and P21 for 8-10V input to do this. Please use the upmost care in doing this. Make sure the board is sitting on an insulated background (glass/wood etc.). Of course you will want to configure the IOBYTE to the USB port or VGA and PS2 keyboard.

Parts

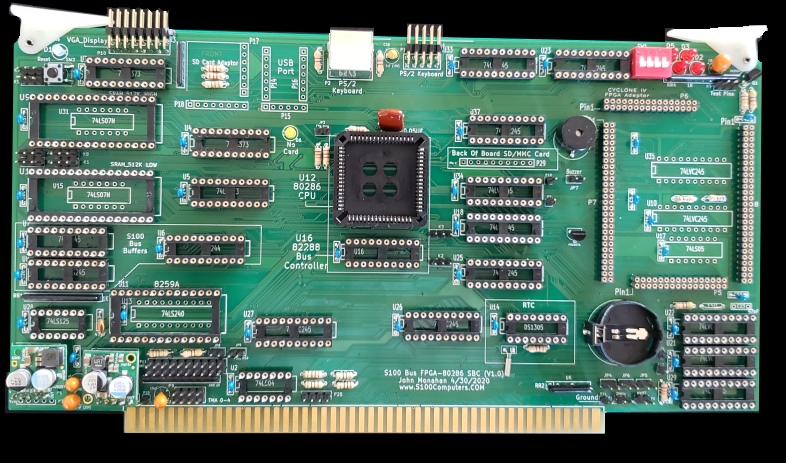

There appears to be a few variations of the 74LVC245 20 pin DIP level Shifters chips with "A", "AN" etc. after the 245. As best I can tell so long as they are 20 pin DIPs they are all OK. I use Mouser chips # 595-SN74LVC245AN.  |

|

This page was last modified on 05/08/2020