| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

Morrow S-100 Boards

24K RAM

64K RAM

Disk Jockey FDC

Multi I/O

SuperRAM

SwitchBoard

Z80 Board

Hard Disk Controller

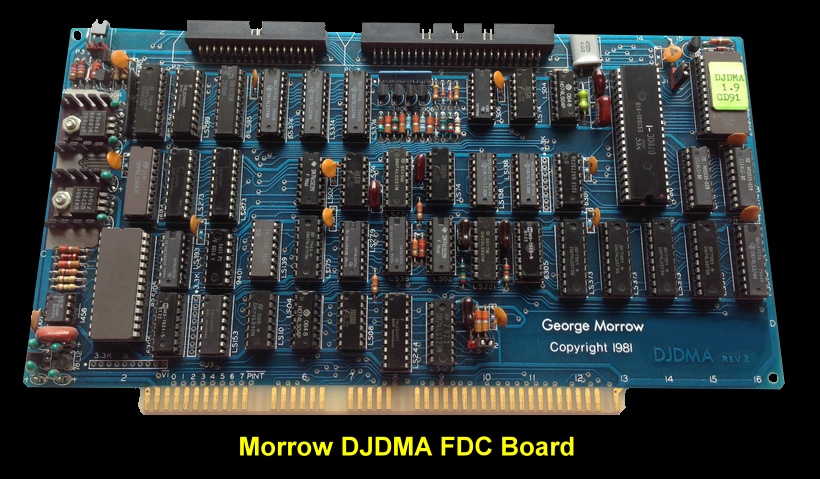

DJ-DMA FDC

8K DRAM

HDC-DMA Controller

This page was last modified on 05/04/2016