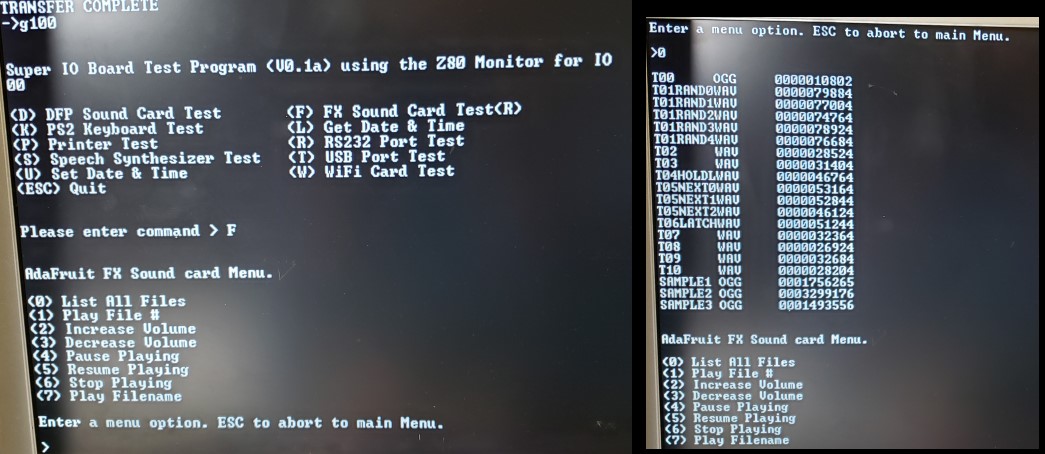

What is mean by trigger effects? Well, depending on your project you may

need to have audio play in different ways. Adfruit thought of the five

most common needs and built it into the Sound Board -- so you just

rename the file to get the effect you want.

See the product tutorial for more details

- In summary:

- Basic Trigger

-

name the file Tnn.WAV or Tnn.OGG

to have the audio file play when the matching trigger pin nn is

connected to ground momentarily

- Hold Looping Trigger

- name the file TnnHOLDL.WAV

or .OGG to have the audio play only when the trigger pin is held

low, it will loop until the pin is released

- Latching Loop Trigger

- name the file TnnLATCH.WAV

or .OGG to have the audio start playing when the button is pressed

momentarily, and repeats until the button is pressed again

- Play Next Trigger

- have up to 10 files play one after the other by naming them TnnNEXT0.WAV

thru TnnNEXT9.OGG.

Will start with #0 and each one on every momentary button press

until it gets through all of them, then go back to #0

- Play Random Trigger

- just like the Play Next trigger, but will play up to 10 files in

random order (TnnRAND0.OGG

thru TnnRAND9.OGG)

every time the button is pressed momentarily

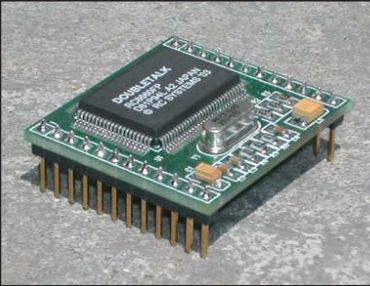

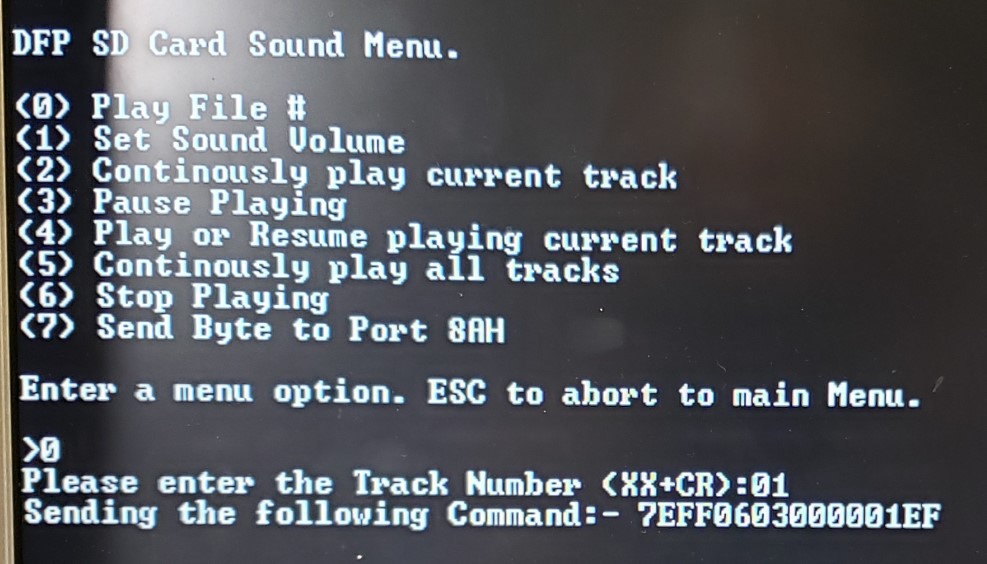

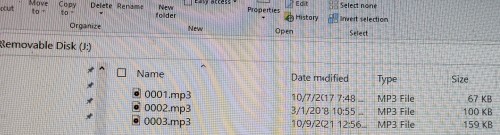

The sound board is designed to be simple: it does not have

polyphonic ability, can't play

MP3's

(MP3 is patented and costs $ to license, so

this board uses the similar but not-patented

OGG format,

there's tons of free converters that will turn an

MP3

into

OGG), isn't

reprogrammable or scriptable, and you can't have any other kind of

trigger type. However, there's a good chance the project you want to

make will work great.

Adafruit designed this board specifically for people who wanted to

make props, costumes, toys, and other small portable projects.

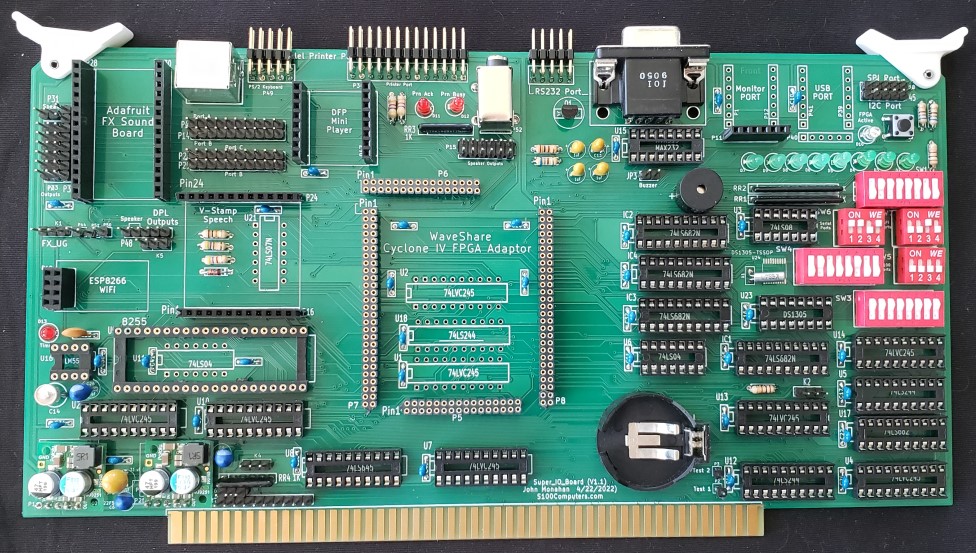

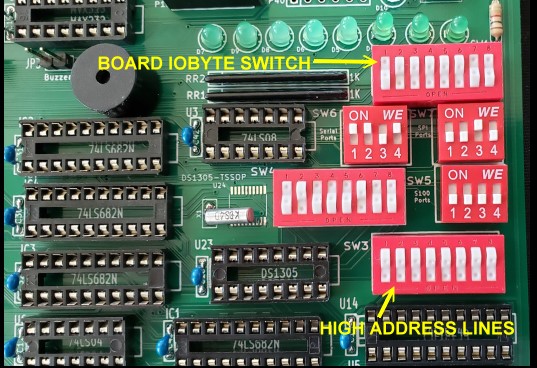

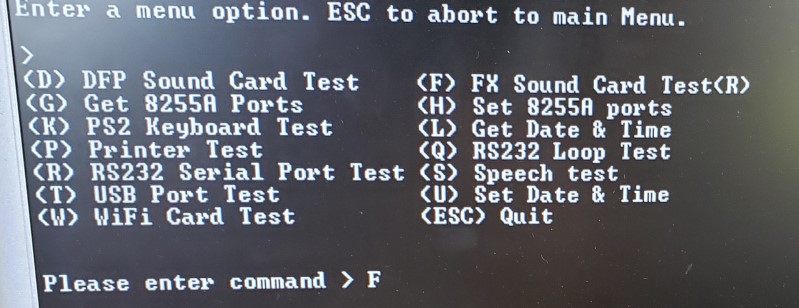

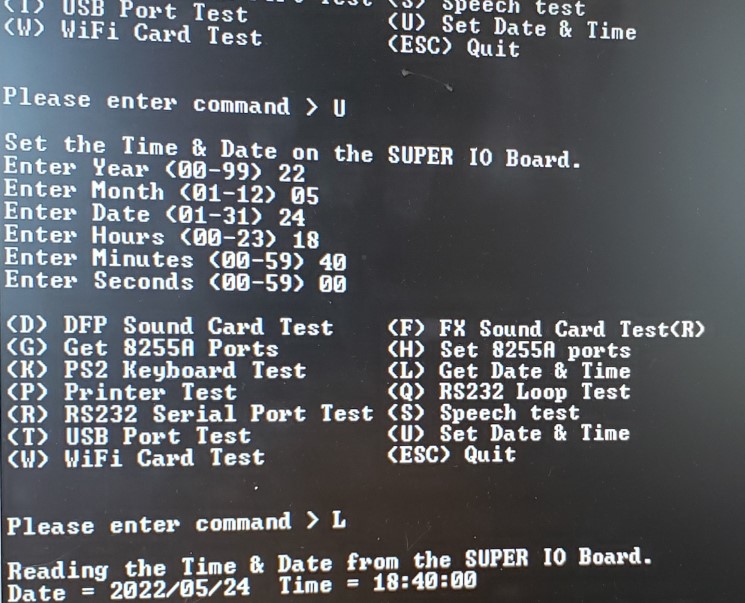

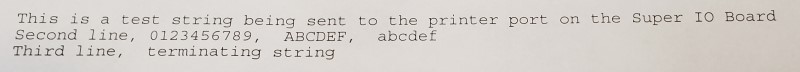

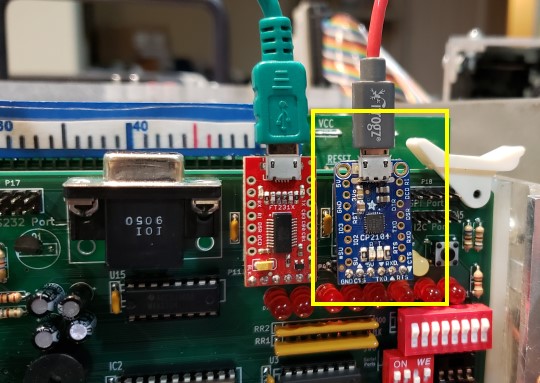

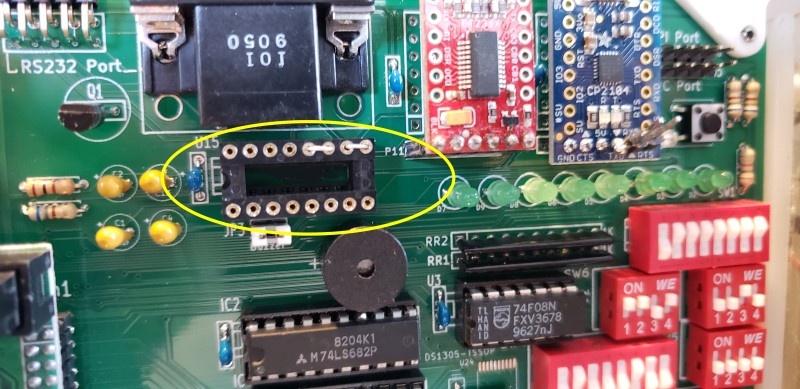

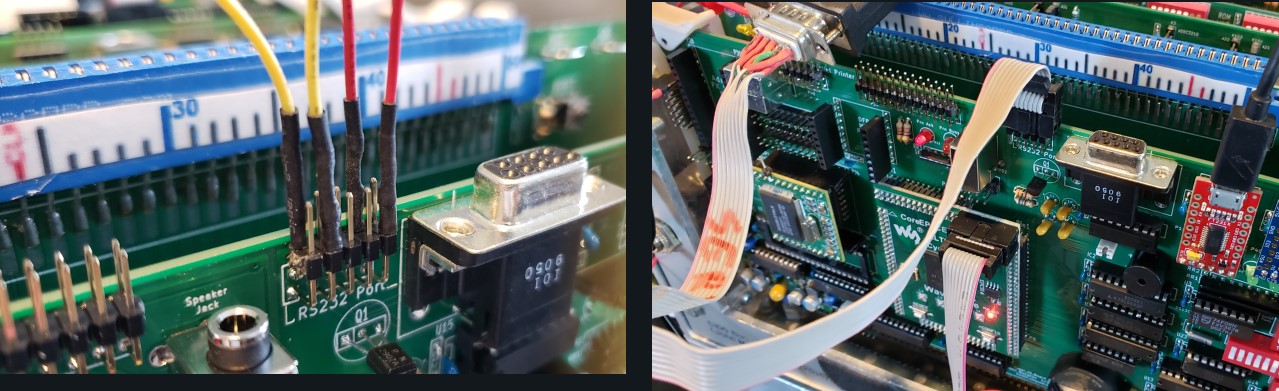

Please note that I have duplicated the 8 printer port pins (p32) along side

the Adafruit FX Sound Board p33 header. With jumpers you can program the

sound output as described by Adafruit. Just send/set bits on the

printer port (without sending the printer strobe pulse of course).