| |

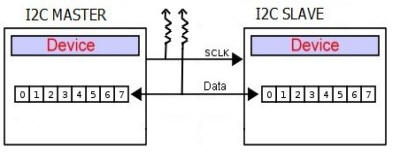

I2C can be multi-master and multi-slave, which means there

can be more than one master and slave attached to the I2C bus |

|

SPI can be multi-save but not a multi-master. That means

there can be only one master attached to the SPI bus. |

| |

I2C is a half-duplex communication protocol |

|

SPI is a full duplex commination protocol. |

| |

I2C has the feature of clock stretching, that means if the

slave cannot able to send fast data as fast enough then it suppresses

the clock to stop the communication. |

|

Clock stretching is not possible with SPI. |

| |

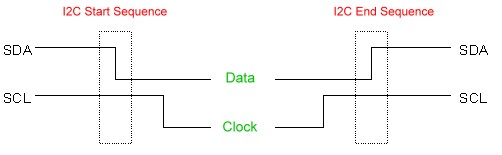

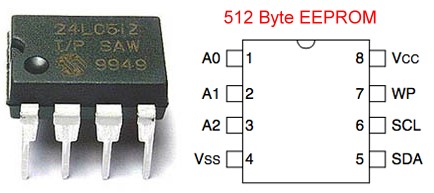

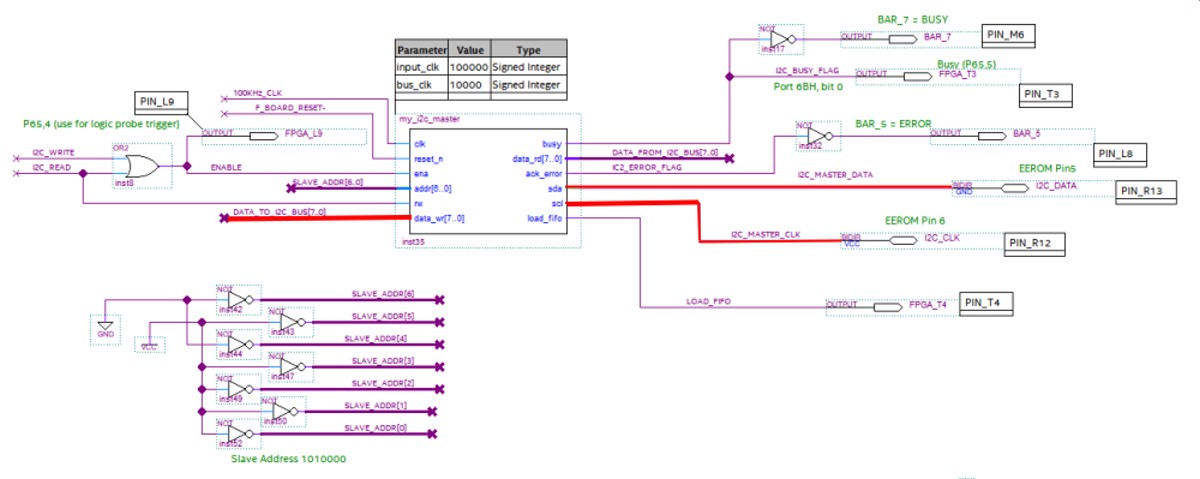

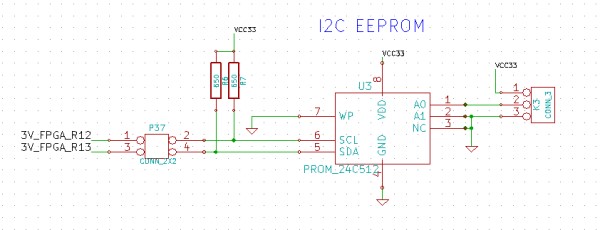

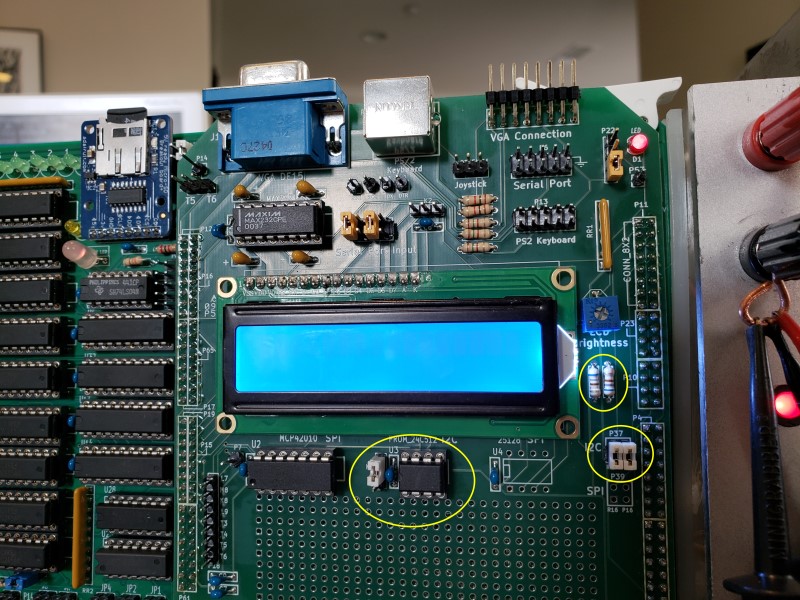

I2C uses only two wires for the communication, one wire

is used for the data and the second wire is used for the clock. |

|

SPI needs three or four wire for communication (depends

on requirement), MOSI, MISO, SCL and Chip-select. |

| |

I2C lines require pull-up resistors. |

|

There is no requirement of

a pull-up resistor in case of the SPI. |

| |

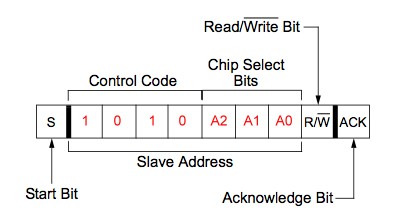

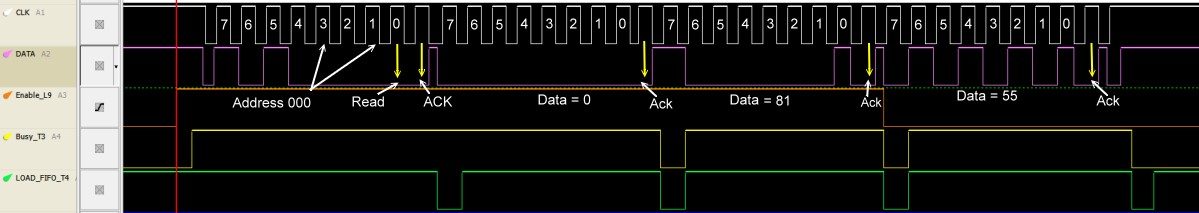

In I2C communication we get an acknowledgment bit after

each byte. |

|

Acknowledgment bits are not supported by the SPI

communication protocol. |