The FPGA 80486 board, when completed following the build instructions

below, will function as a slave CPU. Therefore while building and

testing this board you must have the following boards installed in your

system:-

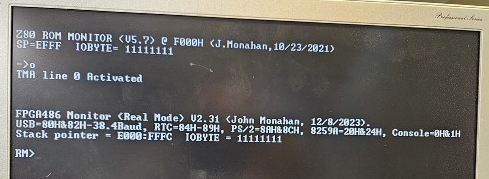

1. Either the "

Z80 Master

CPU board", "

Z80 SBC board",

or "

Z80 FPGA SBC

board". The instructions below assume you are using the "Z80 Master

CPU board". If you have one of the Z80 "SBC" boards the monitor program

on those boards lacks an "O" command to perform a swap to the 80486

slave CPU, and you will need to use the monitor to manually perform an

Input from port

EDH

to initiate the processor swap (QIED).

The System Monitor board

needs to be present for when an input from its port

EDH lowers the

TMA0 S100 bus

line. P30 3-4

must be jumpered. Without the System Monitor board you can "force" this

FPGA_80486 board to slave mode by jumpering

P30 1-2 and

K5 1-2.

Remember TMA0

must be low for this board to take control of the bus.

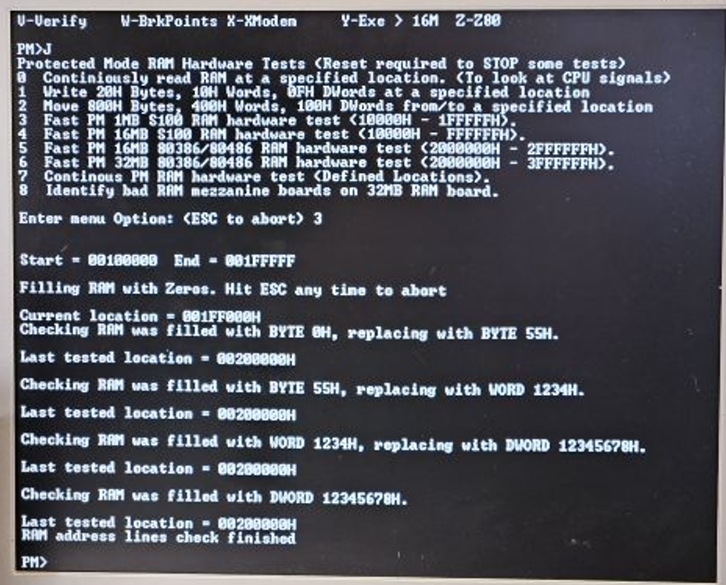

2. An S100 RAM board with a minimum of 64K, which will already be

installed in your system if you are using the "Z80 Master CPU board". If

you are using one of the Z80 "SBC" boards and their on-board RAM, you

will need to install an additional separate S100 RAM board with at least 64K.

3. Having a "

Propellor

Console Board" installed in your system is not essential, but it

will make the initial build steps of the FPGA 80486 board much easier.

If your system does not have a "Propellor Console Board" you will be

unable to communicate with the FPGA 80486 board until after the USB

serial port interface has been installed, several steps into the build

process. Alternatively see if you have a console IO interface that can

be configured like the

Propellor Console Board (Status Port 0. Data Port 1) and the same status

bits you could use it.

4. During initial building and testing of the 80486 FPGA board, it is

recommended all boards be removed from your system with the exception of

the three boards listed above. If your system has an S100 Bus SMB and/or

Bus Display Board installed - those boards can be left in place.

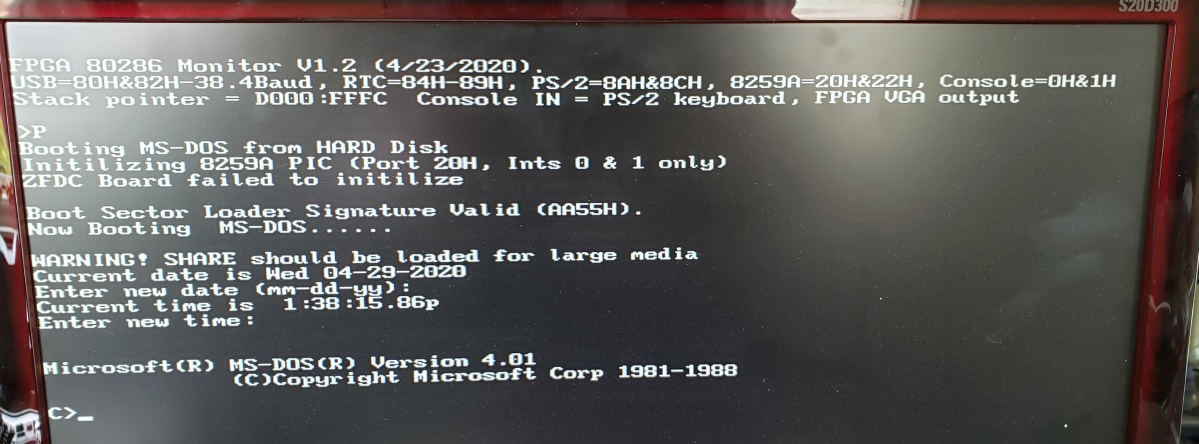

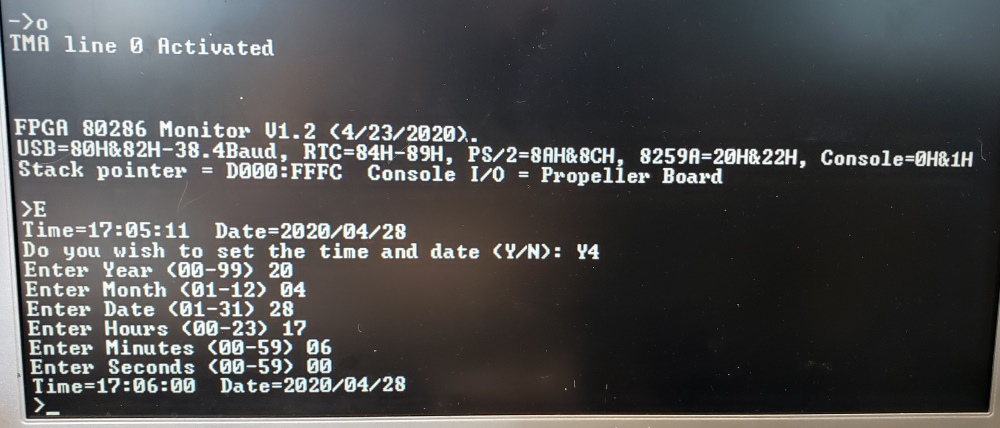

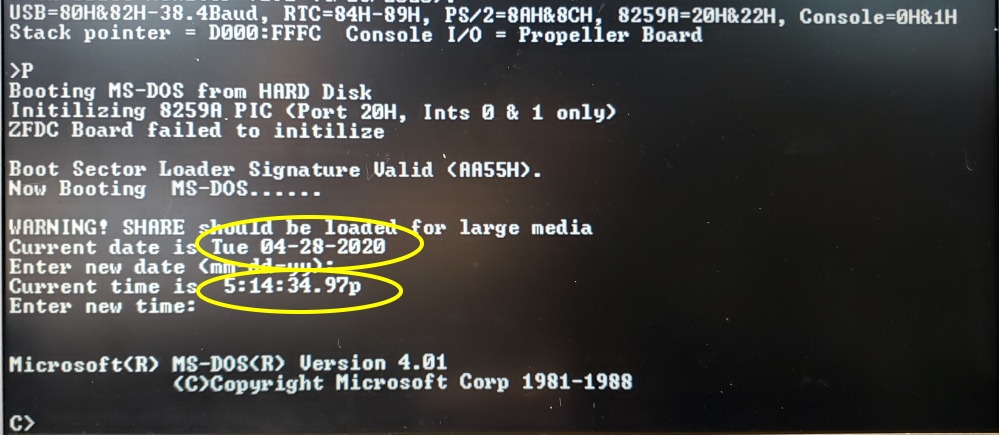

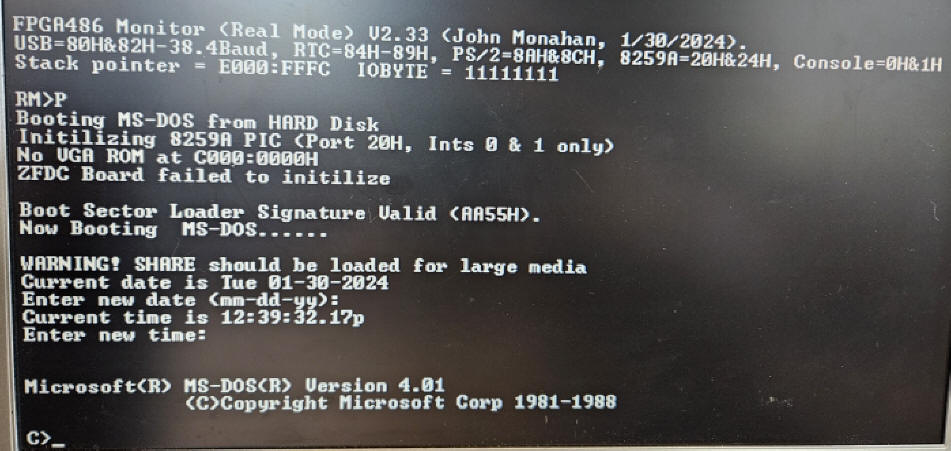

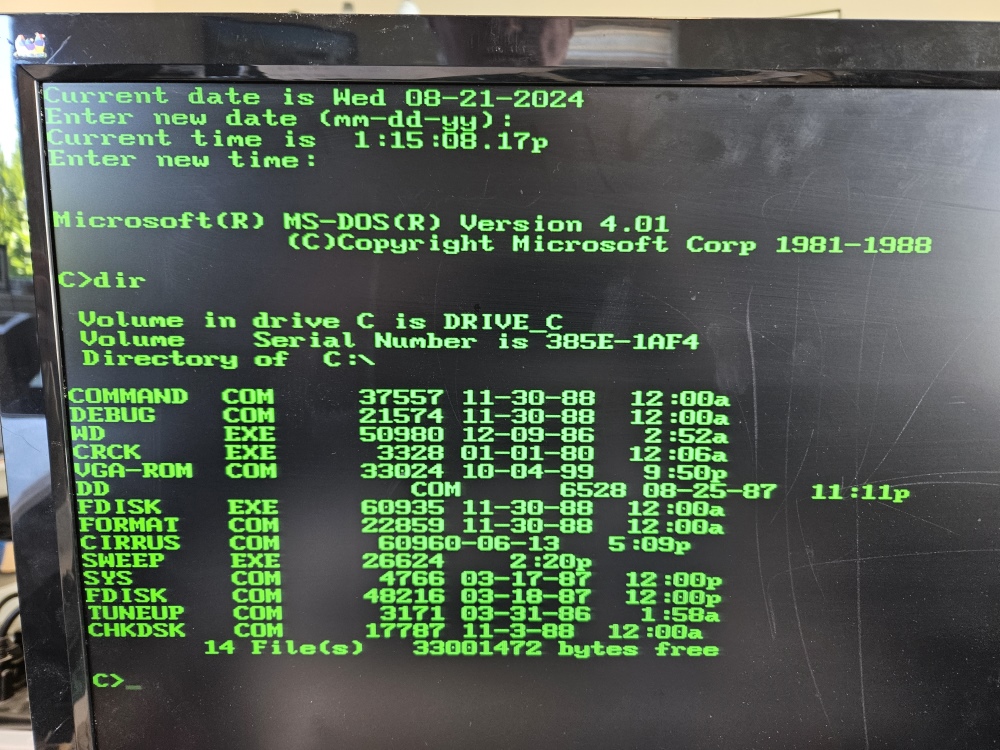

5. At the step below "The RTC Circuit" your 80486 board will be ready to

boot MSDOS. A "

CF/IDE board"

will need to be installed in your system at this point, allowing you to

boot MSDOS from card "B" on the CF/IDE board. Note that (a) the FPGA

80486 board cannot boot MSDOS from the CF card on either of the Z80 SBC

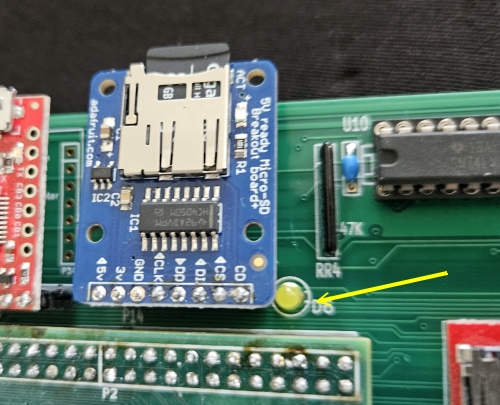

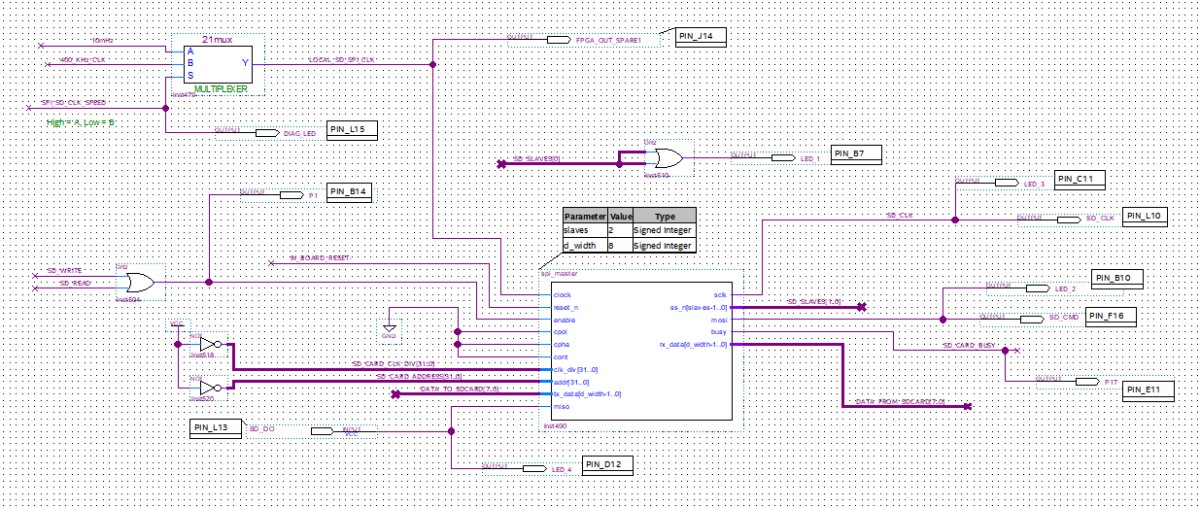

boards and (b) since software support for the SD cards on this FPGA

80486 board is incomplete.

6. This FPGA 80486 board has most of the key functions of the

MSDOS Support board

built in, so a separate MSDOS support board is not required to run

MSDOS.

7. Currently software to boot MSDOS from either of its on-board SD cards

is not written. You need to use the

IDE/CF card board.

The MSDOS card must be in drive B: (A: is always for CPM3). MSDOS

can be downloaded from

here.

8. It is recomended you place your S100 bus RAM board next to this

board in the bus.

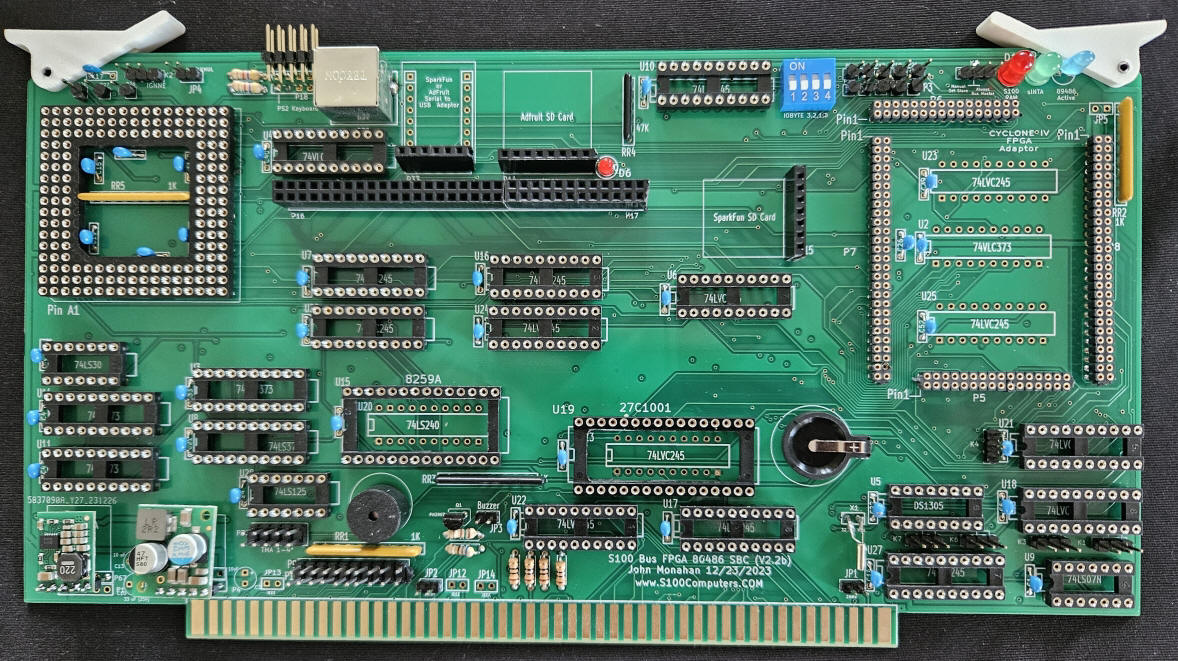

Step By Step Building the

FPGA 80486 SBC Board

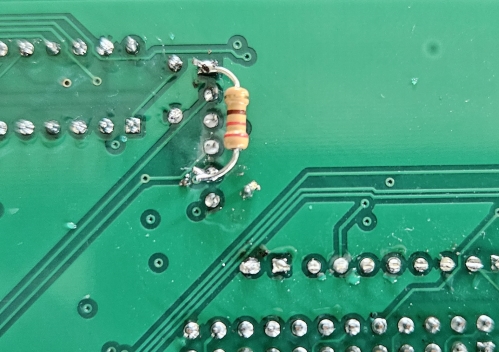

The build instructions are fairly simple for this board but because it is a complex board building it should not be rushed. As always, first examine the bare board carefully for scratches or damaged traces, use a magnifying glass if need be. A broken trace is almost impossible to detect by eye on a completed board.

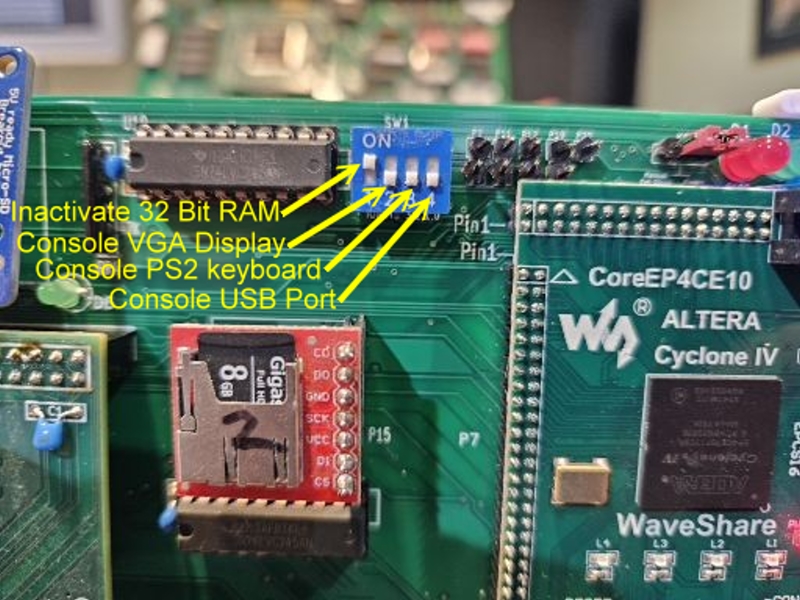

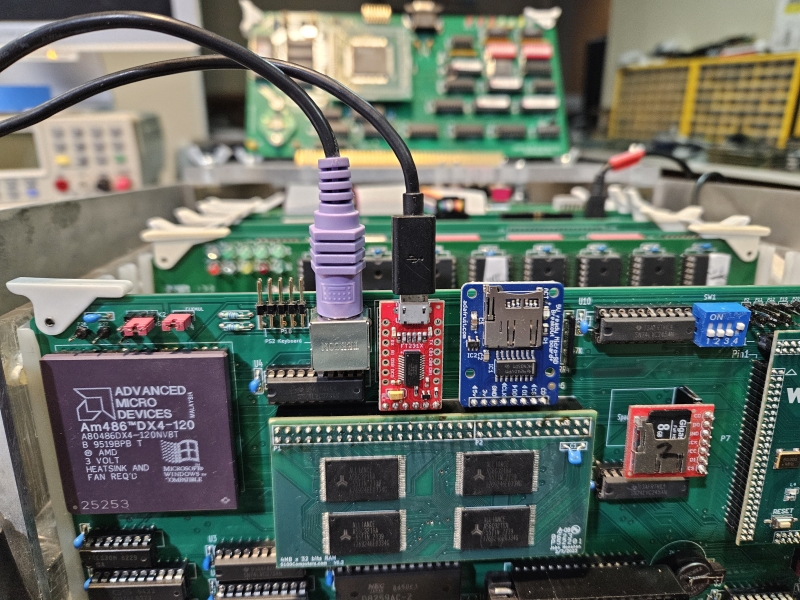

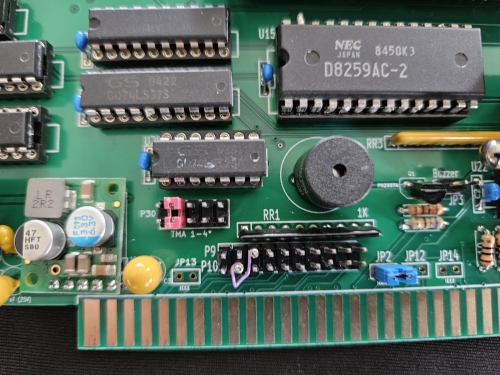

Solder in all the required IC sockets,

resistors, resistor arrays, capacitors, jumpers, and the Pololu 5V and 3.3V voltage regulators. Also do not add

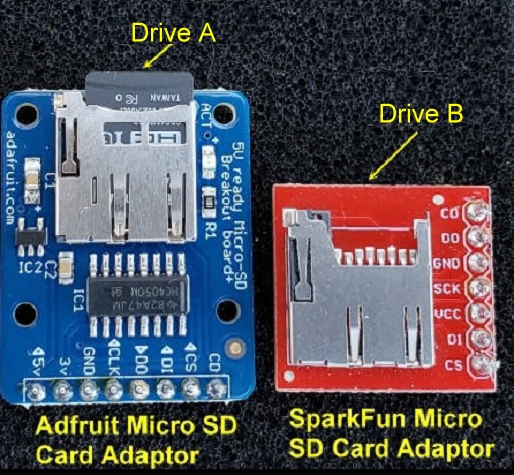

the MicroSD Card Adaptor yet. Please be sure you put the

resistor arrays in with the correct orientation of pin 1. An incorrect

orientation is one of the most difficult things to detect/debug on a board

if not noticed. Check their values

before soldering (they are difficult to remove). Insert all jumper arrays.

The holes for the PS/2 keyboard socket are slightly off -- at least for the

Jameco one. The lowest two pins need to be bent slightly. Clip

off the 3 outer shell ground tags. You can just add solder to the outer

shell and the board shell holes when the PS2 pins are soldered in.

Note there are two sockets for the Pololu 5V regulators. While the older ones

(D24V25F5) are still available

and use P1, it seems Pololu is suggesting users use the newer

D24V22F5's

(5V, 2.5 Amp) units, it has a different pinout, use this one in P67. More

recently they also added the equivalent

D24V22F3

3.3V regulators. Use socket pins P24. If you use the older Pololu

D24V