The Parallax 27800 joysticks have a

mechanical limit which restricts the movement to a circular pattern.

For this reason they are scaled to give a +/-4V maximum output so it is

possible to reach the corners such as +2.5,+2.5.

Other joystick units may not have this restriction, in which case it may

be desirable to change the resistors R8 and R14 in the joystick circuit from

100K to 15K ohm, giving a +/-2.7 volt maximum output.

This will produce better resolution for the controls.

In addition to the above original control ports there are several functions controlled by jumpers located on the PC board.

1

Red, Pr, or composite

video from a 75 ohm source. 0.7V

P-P into 75 ohm load with 0.3V negative sync when used.

2

Green, Y, or composite

video from a 75 ohm source. 0.7V

P-P into 75 ohm load with 0.3V negative sync when used.

3

Blue, Pb, or composite

video from a 75 ohm source. 0.7V

P-P into 75 ohm load with 0.3V negative sync when used.

6

Ground return for pin 1 for coax.

7

Ground return for pin 2 for coax.

8

Ground return for pin 3 for coax.

5, 10 Ground

returns for pins 13 & 14.

13 H sync from a 75 ohm

source. +4V baseline open circuit, 0V negative going sync pulses normally.

14 V sync from a 75 ohm

source. +4V baseline open circuit, 0V negative going sync pulses normally.

H and V sync pulses may be

made positive going by putting a jumper on P18 pin 29-30.

When the

TV Dazzler is outputting B/W video (mode 0 0), pins 1, 2, and 3 are independent

copies of the same video signal, and composite sync may be put on all three

outputs by installing jumper P18 pins 27-28.

If this jumper is not present, then only the output on J2 pin 2 will have

composite sync.

When the

TV Dazzler is outputting RGB video (mode 0 0), the sync waveforms are at

standard TV rate and are present only on the G output unless a jumper is placed

on P18 pins 27-28. The H and V sync

outputs may optionally be used by the display if desired.

When the

TV Dazzler is outputting RGB video for a VGA display (mode 1 0), the RGB outputs

are 0.7 V P-P and do not have any sync.

The display uses negative going sync from the H and V outputs.

When the

TV Dazzler is outputting YPbPr video (mode 0 1), the Y signal will have

composite negative going sync on it.

The Pb and Pr signals, being bipolar, will have a 0.65 volt DC baseline offset

into a 75 ohm load. This works

satisfactorily on most component displays.

When the

TV Dazzler is outputting composite video (mode 1 1), then composite sync, burst,

and chroma are present on pins 1, 2, & 3.

All 3 signals are independent copies of the same video and 1.0V P-P into

75 ohms.

All modes use 59.94 Hz rate for vertical sync.

VGA uses 31.469 KHz rate for horizontal sync, and all other modes use

15.734 KHz rate for horizontal sync. The

color subcarrier is 3.579545 KHz, giving NTSC operation.

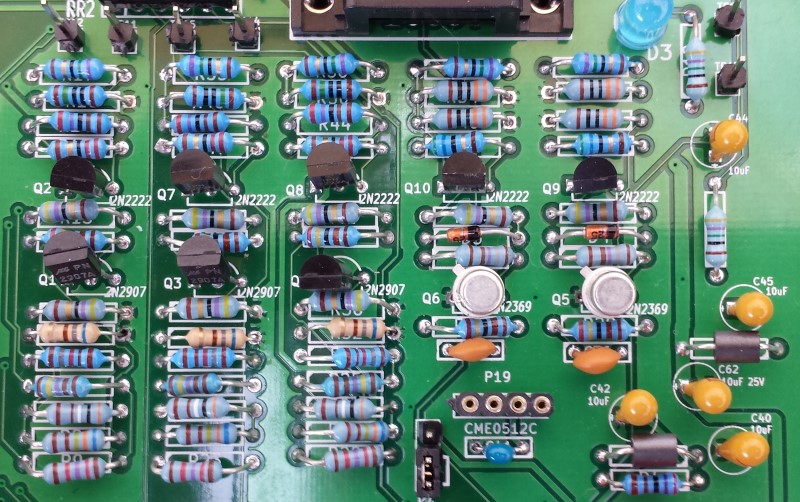

Step By Step Building the Dazzler II Board

The build instructions are fairly simple for this board but because it is a complex board building it should not be rushed. As always, first examine the bare board carefully for scratches or damaged traces, use a magnifying glass if need be. A broken trace is almost impossible to detect by eye on a completed board.

Unlike most other boards on this site, this board has an extensive analogue

signal component. The values of the resistors are sometimes not common,

but those values must be used. All resistors should be within 1% of the

schematic quoted value. All components are available from Mouser/DigiKey

etc.

Build the board up in functional steps. Avoid the temptation of adding everything at once and popping it into your S-100 box. Step by step is faster in the end -- trust me. We will set the board up configured as a self contained video board first independent of the S-100 bus. In this mode we will program the U3 CPLD with a special test pattern to check its functionality. Only when this works will we utilize the S100 bus section of the board.

Solder in all the required IC sockets, resistors, resistor arrays, capacitors, jumpers, and the 5V and

-12 voltage regulators. The -12V,

LM7912 regulator does not need a heat sink but if you use a LM7805 be sure and add one.

The LM7912 however does need a mica insulator between itself and the board as

well as a Teflon bolt. The back of the regulator should not be grounded.

(The square pad where the bolt goes is actually not grounded, but the is a

danger of the nearby board front ground plane shorting through the varnish layer

to the back or the regulator without the mica insulator).

Do not add the LED's yet. Be sure you put the resistor arrays in with the correct orientation of pin 1. Check their values before soldering (they are difficult to remove). Insert all jumper arrays.

For prototype boards I generally use "double swipe" IC sockets. For a critical board like this I prefer to use "Machine Tooled" IC sockets. However they are more expensive and you have to be particularly careful not to bend the IC pins. The two clock oscillators can have their own special sockets (e.g. Jameco #133006) but actually I find the "Machine Tooled" IC sockets make a better connection. I in fact solder the 2MHz oscillator directly to the board since it will never be changed.

Next insert all 3 LED's. Before soldering them in place bring to +5V (D1, & D3) or (-12V ,D2) the appropriate pin to make sure it lights up. I use a blue LED for D3 "Board Active".

Check the voltage to sockets on the board is about 5V by placing the board in your S-100 system using an extender board. With no load you will typically get 5.00V (+/- 0.2V). BTW, your system should boot and run correctly with its Z80 master CPU board. If not, you have a serious solder bridge somewhere on the board. Before you do anything else with a magnifying glass go over every socket on the board and examine for a proper solder joints. I like to "reheat" each joint just to be on the safe side. The silk screen/varnish on these boards us quite thick. It's easy not to have a good solder joint for the ground pins. Double check. Extra time here will save you hours later, (Been there, done that! ).

.jpg)