The board utilized (Cromemco style) bank select capability (IO port 40H) to

allow up to 8 boards to reside in a system. The board is configured as four

16 K blocks, one or more of which can be inactive for any or all boards in

a system. This allowed easy implementation of CPM+. The D.P. computer BIOS

allowed you to use bank 0 for main ROM and banks 1-15 for a RAM disk.

A system running with 2 double sided 8" floppies plus a four board RAM disk

was super fast if you moved your programs and data to RAM

vs.

leaving them on the floppy.

BTW, the BIOS had a few quirks and didn't match the print out that came with

the documentation. As supplied the handshake failed for anything above 9600.

It was a simple matter of changing the handshake overflow test code to test

all pins of handshake serial lines. The format used on the 8" floppy disks

was always single density for the first track and then could be either

single to double density for the remaining tracks. This made swapping with

other computers only possible if you formatted and stored data in single

density.

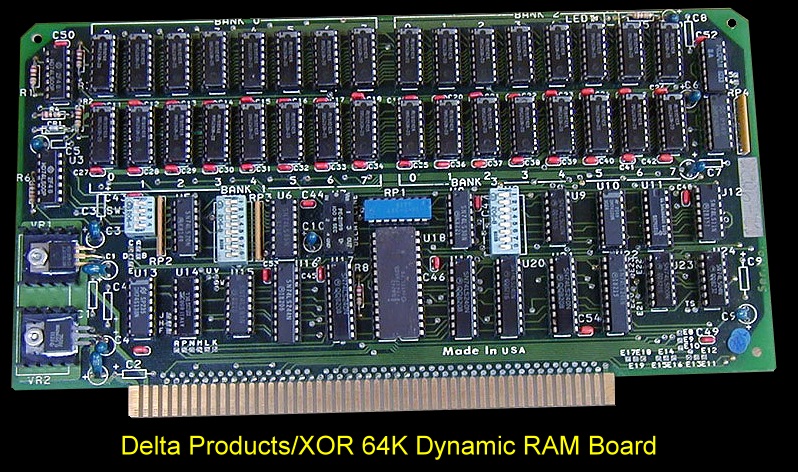

Many if not all of these Delta Products 64K memory

boards also had a common of having the tantalum capacitor for the minus

power voltage installed with the + & - leads reversed and so marked on the

board too. After a period of time the capacitor would from

being install wrong short out the minus power supply and the board would

die. Replacing the capacitor with a new one and having the + lead going to

ground and the - lead going to the minus power would get the board working

again.

Donald Burns added the following notes about this

board:-

There's a second mode of full 24 bit S-100 addressing. All that is needed a

change to some jumpers. The limit on the number of these boards in one

system would be 256 using the full 24 lines of S-100 bus decoding!

Details on the XOR Data Science and Delta Products 64k memory board.

The official XOR Data Science name for the 64K ram board was "64K-DQ"

and the following spec's are listed on the front cover:

Fully bank selectable

I.O. Port 40 (CROMEMCO) compatible bank select

Disable on 16K boundries

On board refresh

DMA compatible

Extended address lines A16, A17, A18, A19 (*** manual explains

how to use A20 - A23 in mode 2 also)

IEEE S-100 design

From the manual the following has been extracted:

The board has a M-1 Wait State Generator for certain asynchronous

events (I.E. DMA disk reads etc.) In normal mode no wait states will be

generated.

Automatic Refresh treats reset and wait states the same, if an

interval counter clocked off PHI 2 reaches 14 the PRDY line (pin 72) is

pulled low and a refresh cycle is done during count 15. Note: XRDY is not

monitored and if XRDY is pulled low memory with forget everything in 2ms.

***

Different Modes:Board Select (Mode one) -- I.O.

Port 40H and up to 8 boards due single bit out of byte for each board

selection via SW-2 (8 position). Jumper E-4 to E-5 must be removed and

Jumper E to B installed and T to S removed to use this mode.

Board Select (Mode two) -- S-100 extended address lines A16 to A23 (8

lines) controlled via SW1 (8 position) . Jumper T to S removed (I'm not sure

if this is correct - T-S jumper per list below enables extended addresses?)

and jumper E to B removed to use this mode. Binary logic on SW-1 allows 1 of

256 board decoding.

Bank disable -- SW3 (4 position) turns off one or more of the

four 16K banks on the board.

List of factory installed (default) jumpers for use with XOR CPU and

all other Z80 cards must be able to provide besides normal S-100 bus signals

two other signals --> memory request/not (MREQ pin 19) and refresh/not (RFSH

pin 28) to be able to run the 64K DQ.

List of jumpers and the function of each jumper if it is installed

(default is in parentheses):

B-C (open) No memory management

E-B (open) I/O port memory manage

T-S (installed) enable extended address

F-H (installed) enable phantom pin 67

F-J (installed) pull up phantomM-K

(installed) MREQ no inversion

M-L (open) MREQ inversion

P-N (installed) use MREQ to start memory cycle

P-R (open) use MWRT+SMEMR to start cycle

V-U (installed) Ignore A20, A21, A22, A23 address lines

V-W (open) use all extended address lines

E8-E9 (installed) reset I/O port latch on PR75

E8-E10 (open) reset I/O port latch on SLV 54

E16-E15 (installed) RFSH no inversion

E16-E14 (open) invert RFSHE19-E18

(installed) RFSH on pin 66

E19-E17 (open) RFSH on pin 66 (??????)

E22-E21 (installed) no inversion of PHI to counter

E22-E20 (open) invert PHI 2 to auto RFSH

E23-E20 (installed) invert PHI to RFSH cycle flop

E23-E21 (open) no inversion of PHI 2 to RFSH

Phantom Line

All memory banks will become disabled when S-100 bus pin 67 is pulled

low. To disable this feature, cut trace between F to H.