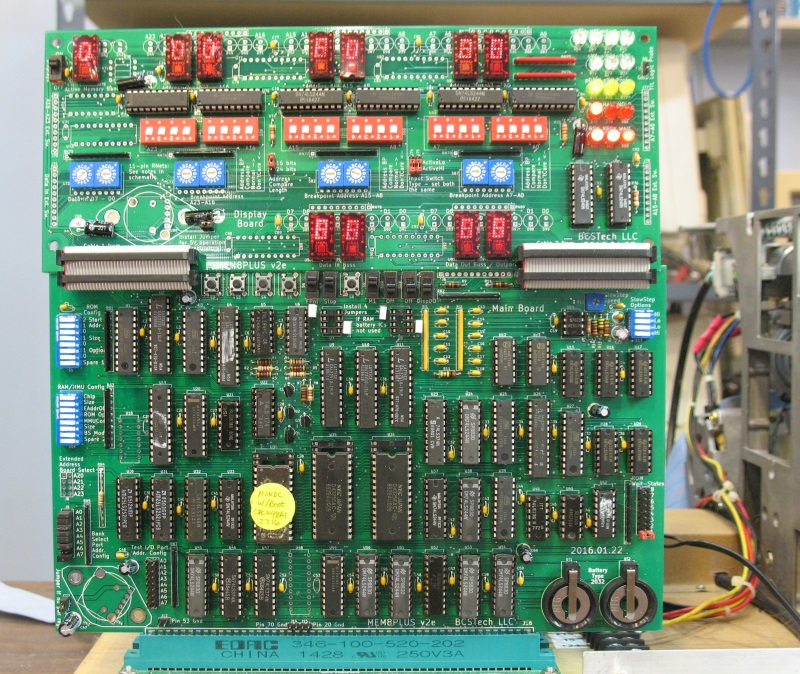

- System Monitor Option: This is the base of the PLUS features. No other PLUS options are possible without this. When fabricated, the MEM8PLUS board is actually two boards that are initially attached to each other. First is the 10” by 6” S-100 Main Board. (Yes, 6 x 10 is one inch higher than the standard, but it is still within the IEEE-696 specification, and the extra inch provides space for some front panel components that need to be accessible when the board is plugged in.) This contains all the components to operate the MEM8 part of the design, plus many of the parts of the PLUS section. Then, on top of the Main board is a 10” by 4” board called the Display Board. The two may be used as-is, or, for certain physical configurations, like bringing the displays on the display board to a front panel, they may be snapped apart and then connected together with two inexpensive 40-pin ribbon cables. The display board, in its minimum configuration as a systems monitor board, has 16 LEDs or four hexadecimal displays to show the contents of the Address bus, 8 LEDs or two hexadecimal displays to show the contents of the Data Input bus, 8 LEDs or two hexadecimal displays to show the contents of the Data Output bus, and 15 LEDs to show the important status and control signals on the bus. A switch on the board turns the displays ON or OFF.

- Extended Address System Monitor Option: This adds 8 LEDs or two hexadecimal displays to show the contents of the extended address bus, A16 to A23. This option would be useful when the 24-bit memory option (described above) is selected, or the Memory Management option is installed.

- Logic Probe Option: A simple TTL logic probe is provided. It reads only TTL levels and displays on a single LED.

- Front-panel Operations Option: This option extends the System Monitor Option to a fully-functional front panel. All these features are enabled by this option:

- Hardware CPU Stop and Start. A switch, when set to STOP will stop the running CPU on the next machine (M) cycle. When set to RUN, the CPU will start running again at full speed.

- A momentary pushbutton switch will step the CPU one M cycle when the CPU is stopped.

- Single-Step by M1 or any M cycle switch. When this switch is set to M1 stepping mode, and the Step switch is pressed, the CPU will be permitted to run until the next M1 cycle where it will stop. In the any M cycle stepping mode, the CPU will stop in the next M cycle, regardless of status. This can be used to view non-M1 memory read, memory write, Input and Output port operations and Interrupt Acknowledge cycles.

- Full or variable speed slow-step selected by switch. When set to full-speed, the CPU runs at full clock speed. When set to variable speed, the CPU will automatically step at a user-selectable rate from as low as about one cycle every 5 seconds, up to several hundred cycles per second.

- Hardware 16 bit address breakpoint with enable/disable. A switch controls this feature. When set to disable, no hardware breakpoints are triggered. When set to enabled, the hardware will stop the CPU when the address set in the breakpoint switches is encountered. This feature will break regardless of the location of the code: any on-board RAM or ROM. There are several sub-options:

- 24-bit address breakpoint is a build option. When installed, a jumper permits selection of either 16-bit or 24-bit operation.

- Three switch options are available during build for setting the breakpoint address (one must be selected):

- Standard 8-position DIP switch.

- Rotary hexadecimal switch. These make setting addresses very easy. They come in active high and active low versions. Either can be used. Different pull-up/pull-down resistors are required and two jumpers must change between the two options. Details are in the schematics and the construction notes.

- External via headers. The user can use any available or desirable SPST switches. They can be wired in either active-high or active low (but all must be the same), and like the rotary hex switches, there are resistor and jumper considerations.

- Range switches - these switches will enable setting an address range for the breakpoint. This is done by permitting each and every bit (16 or 24) to be designated as “don’t care”. For example, if a 16-bit breakpoint is set to F663, and the two least significant bits are set to “don’t care”, then a break will occur on F660, F661, F662 or F663.

|

|

- An 8-bit output “test” port that can be written by the CPU and displayed on the data out bus display. It can be addressed at any 8-bit I/O port. A switch is used to select if the output port or the data out bus shows on the display.

- An 8-bit input “test” port that reads a set of 8-bit data input switches on the display board. It uses the same port address as the output test port. The data input switches have the same dip-switch, hex rotary or off-board options as the breakpoint address switches discussed above.

- Memory Examine, Memory Examine Next, Deposit and Deposit Next pushbutton switches are provided to enable low-level memory operations when the CPU is stopped. These switches are available to the user when the Front Panel enable switch is moved from Normal to Front Panel. These functions operate directly with the on-board memory. The breakpoint set switches double as memory address switches for these functions, and data for the deposit operations are taken from the 8-bit data input switches described previously in the “test” input port feature.

- All front-panel control switches are self-contained and easily accessible at the top edge of the main board using miniature tactile push-button switches and miniature slide switches. Optionally, they can be duplicated on an external control pod or with switches mounted on the front of an enclosure. A header is provided for this possibility.

- For 8080, 8085 and Z80 processors only, a program run function is provided that can force the CPU to any location in memory and have it begin execution there. Existing switches are double-purposed to allow the operator to set a 16-bit start address, and optionally, a memory bank. Then the program can be started at that address in stopped, slow-stepped or full-speed execution modes. Along with the memory examine and deposit functions, complete programs can be “toggled” into the computer at any memory address and run from there, even without a terminal of any kind or a monitor program ROM.

|

|

.jpg)