| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

|

|

|

|

|

|

|

|

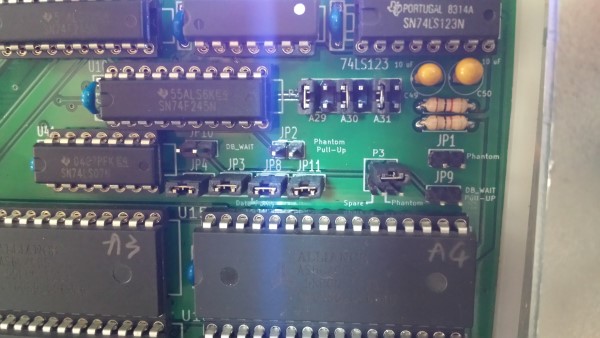

A31,30,29,28,27,26,25,24,23,22,21,20,19,18,17,16,15,14,13,12,11,10,

9, 8, 7, 6, 5, 4, 3, 2,

1, 0 0 0 0 0 0 0 0 1 0 0 0 x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 1 0 0 1 x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 1 0 1 0 x x x x x x x x x x x x x x x x x x x x x 0 0 0 0 0 0 0 1 0 1 1 x x x x x x x x x x x x x x x x x x x x x |

|

|

|

This page was last modified on 11/30/2017