|

| Home | S-100 Boards | History | New Boards | Software | Boards For Sale |

| Forum | Other Web Sites | News | Index |

|

|

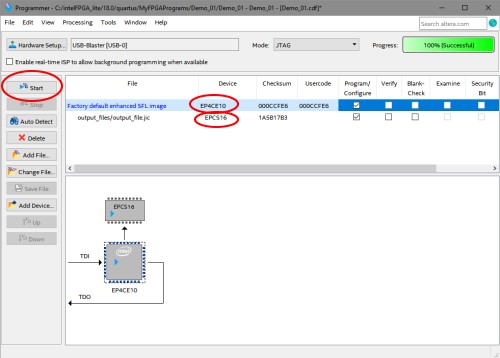

On Intel's own discussion forum are several threads on

the topic of solving the "outdated driver signature problem", specifically

on how to obtain and install the correct updated driver. This properly

solves the issue of device manager not installing the driver for the

Blaster, and Quartus not being able to see the Blaster. I too encountered

this issue when I first installed Quartus on Windows 10 about 6 months ago,

and though the process is a pain to follow it does solve both issues.

On Wednesday, January 26, 2022 at 5:23:27 PM UTC-8

michae...@gmail.com wrote:

Following up on a discussion tonight, I found this

helpful to get the USB Blaster running on windows.

Quartus USB Blaster

You first have to disable driver signature enforcement.

This is the sequence:

1 - Go to windows 10 settings and search for "advanced

startup options"

2 - Under Advanced startup, hit "Restart now"

3 - After a moment, you'll get a "choose an option"

screen - choose "Troubleshoot", then "Advanced options", then "Startup

Settings"

4 - You'll get a screen telling you what you will be

able to change and a single "Restart" button - press it.

5 - If your boot drive is BitLocker encrypted, you'll

need to enter the recovery key (press return, enter the key in the text box

then hit return again - it took me three goes to realize I had to hit return

before I could enter they key !)

6 - You'll be given a menu of options, number 7

disables driver signature enforcement

7 - When the PC restarts, use Device manager to update

the drivers - this time you'll get a warning about the signature, but they

install fine.

8 - When you've finished, restart normally to re-enable

signature enforcement

|

|

|

|

||

|

|

||

|

|||

|

|

|

This page was last modified on 10/20/2022