In 1976, designers at Motorola began working on a 16-bit microprocessor to compete with the Intel 8086 CPU. Their focus was software more than hardware. The wanted to have a CPU with internal 32 bit registers and an external 16 bit interface. Unlike Intel, they wanted to eliminate any special-purpose instructions and allow the microprocessor to perform all operations, on all registers, on all data types, and in all addressing modes. Assembly language programmers like this because it means they don't have to memorize a bunch of exceptions to the instruction set. However this advantage was limited because the bulk of code programming even at that time, was above this level of detail. That said, the 68000 leant itself to UNIX style systems. There were a number 16 bit 68K CPUs, but none really became successful like the Intel 16 bit CPUs. If it were not for the Apple Macintosh, the 68000 CPU would have probably have ended up like some of its relatives, the Zilog 8000 or National 16032.The 68000 could address 16 MB of physical memory with byte resolution. Address storage and computation used 32 bits, however, with the high-order bytes were ignored due to the physical lack of pins. This allowed it to run software written for a flat 32-bit address space. Motorola's intent with the internal 32-bit address space was forward compatibility, making it feasible to write 68000 software that would take full advantage of later 32-bit implementations of the 68000 instruction set.

This happened in 1984 when Motorola came out with its full 32-bit extension to the 68000, the 68020. Initial clock speeds were 12 MHz but this later went up to 33MHz. It had one neat feature, you could dynamically choose the bus size you want 8, 16, or 32 bits with two external pins on the chip. This for example allowed you to use a single boot ROM instead or 2 (or 4) as was the case in the with 16 bit wide systems. They also picked up on the Intel idea of bus buffering by using an efficient "cache". The cache in the 68020 was 256 bytes deep and works a little differently from the 8086 queue. If a jump occurs to a point outside the queue, the queue was flushed and reloaded. But the cache looks just like memory, so a jump to a point in the cache would not cause the cache to be dumped and reloaded. If loops are small enough, they can execute directly from the cache.

T

here was 68010 but it was really a patched bug repaired version of the 68000 that was supposed to work with Motorola's memory management chip (68451). Suffice to say there were problems.

The 68020 added many improvements to the 68000 including a 32-bit external data bus and address bus, and a number of new instructions and addressing modes. There were also some minor improvements and extensions to the supervisor state. The 68020 had a coprocessor interface to incorporated a paged memory management unit (MC68851 PMMU) or a floating point unit (MC68881 or MC68882 FPU) . There was the capability to do bigger multiply (32×32→64 bits) and divide (64÷32→32 bits quotient and 32 bits remainder) instructions, and bit field manipulations were improved.

Unlike its 8086 cousins the 68000 could only access word (16 bit) and long word (32 bit) data if they were word-aligned. The 68020 finally had no alignment restrictions on data access. However, unaligned long word accesses were often much slower than aligned accesses, as was the case for the 8086.

The 68030 was released in 1987. It had an on-chip memory management unit (but still did not have a built in floating point unit). This was added with the 68040 which was released in 1990. It could only reach a speed of 40 MHz because of severe heating problems. Unfortunately the 68040 did not have 8 bit bus capability. The 68020, 30's and 40's were all used in the Apple Macintosh II and later PC lines as well as Sun 3 workstations. The 68030 was the last 68xxx CPU to have 8,16 or 32 bit dynamic range bus addressing capability. For this reason we will go with a 68030 CPU board.

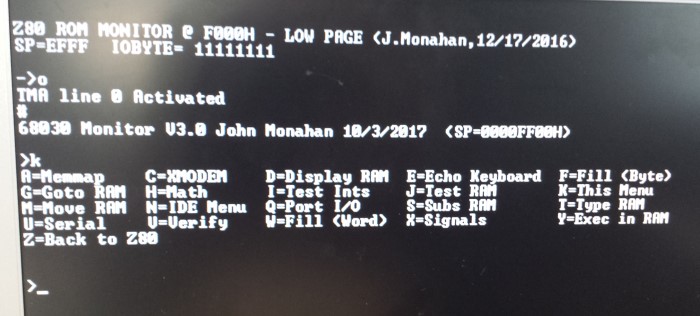

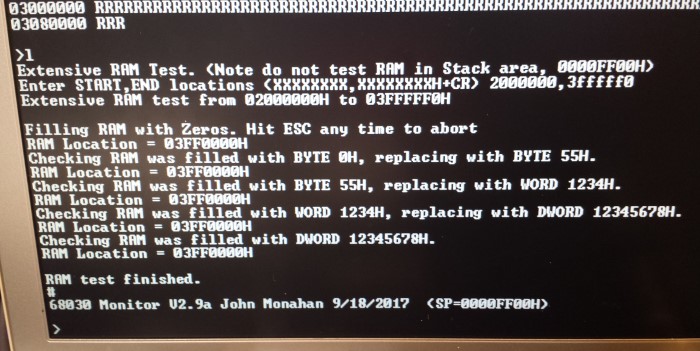

From the assembly language programmers point of view the 68030 is a real joy to program. Upon power up you immediately have use of all the 32 bit registers and a continuous memory plane of 4GB starting from 0H in RAM. All the registers are symmetric with no "special cases".

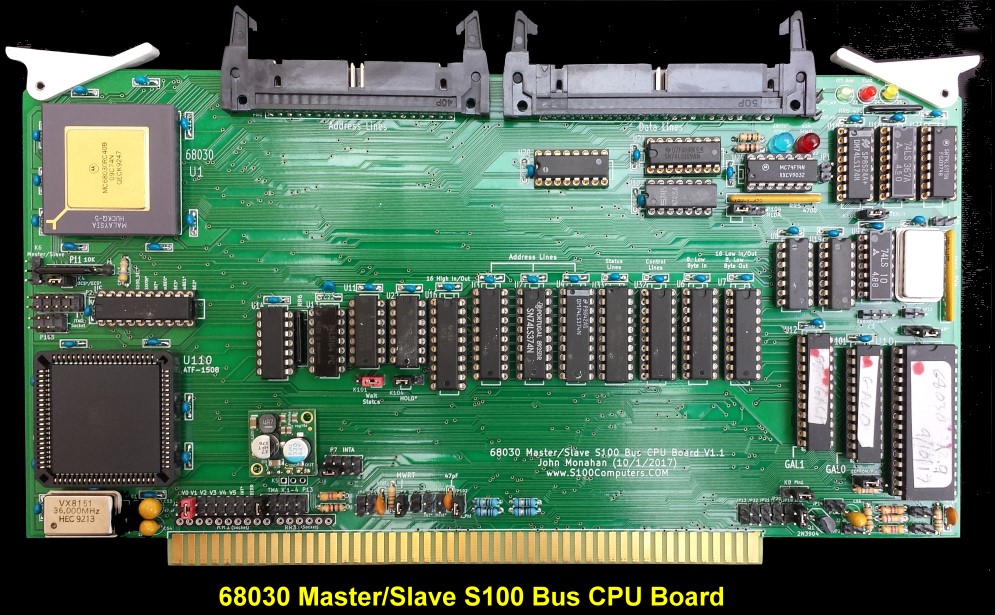

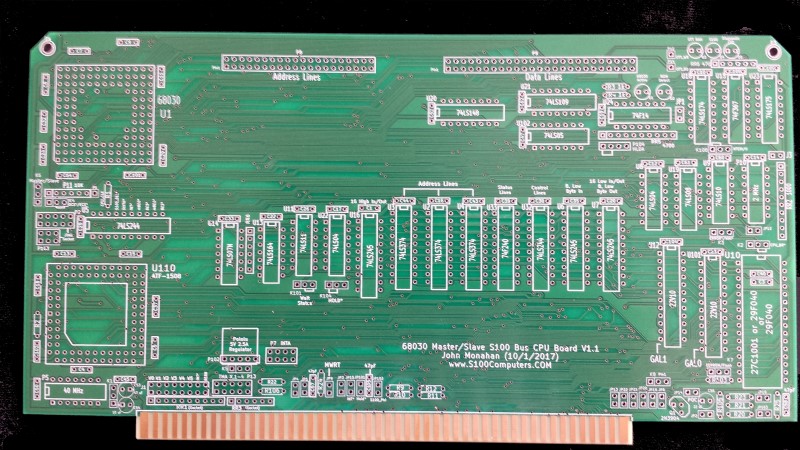

I should point out also that typically when I start a completely new S100 CPU board I anticipate many hardware problems. The 80386/80486 boards took over a dozen prototypes to get working fast and reliable and almost a year of work. Admittedly I had that knowledge and experience beforehand with this board, but only 3 prototypes were required -- and two of these were obvious errors on my part.

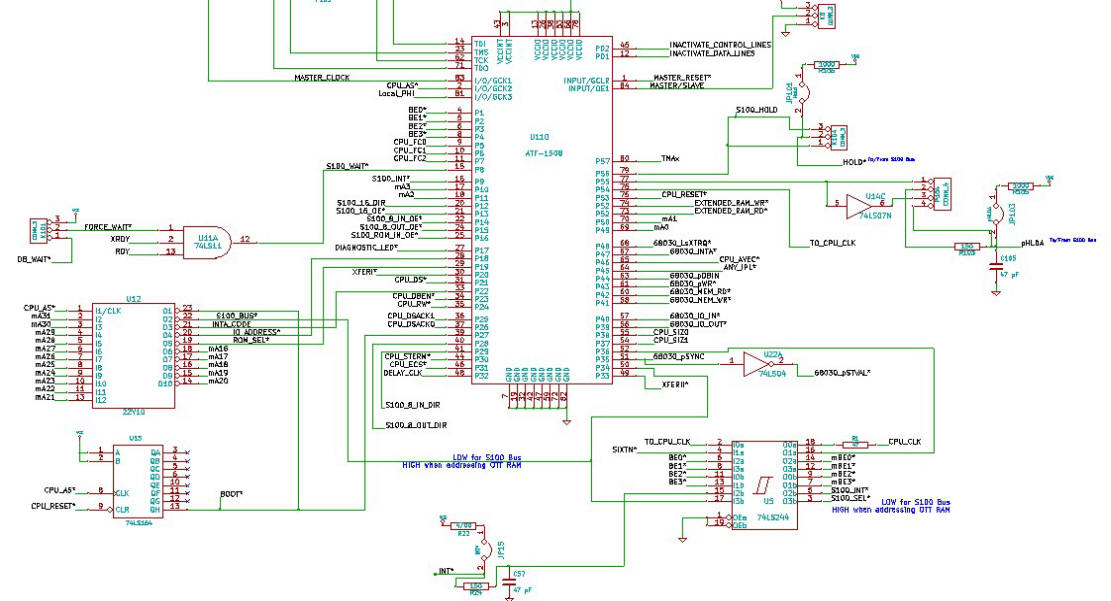

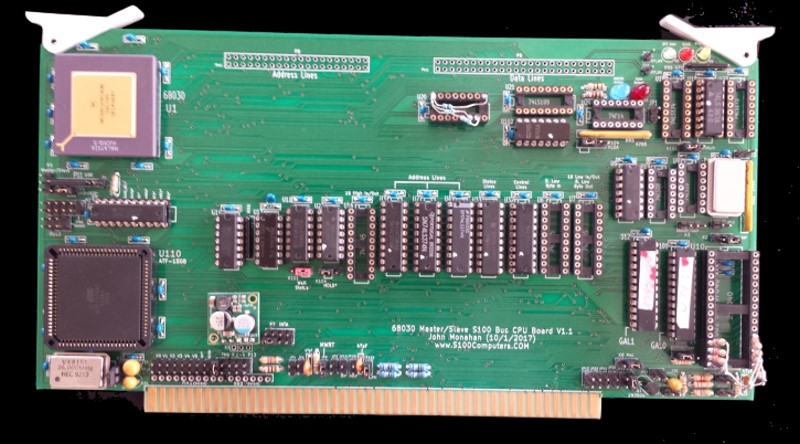

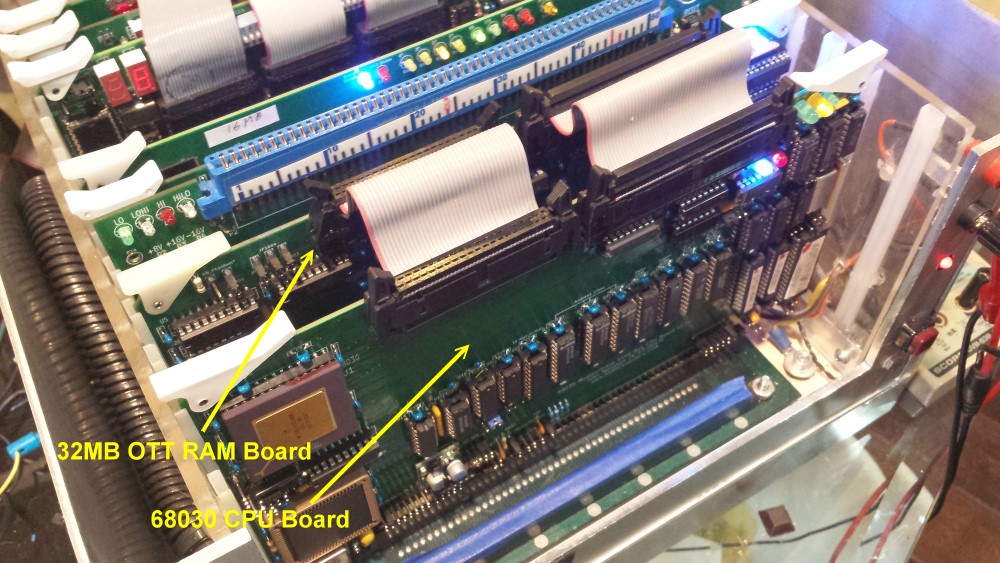

As for our 80386/80486 CPU boards we will use the same format of using a single 1508 CPLD to convert the Motorola CPU signals into an S100 bus format. As before we will use one optional 22V10 GAL to switch the bus Master/Slave configuration and another to identify where the OTT RAM is located in the 4 GB address space.

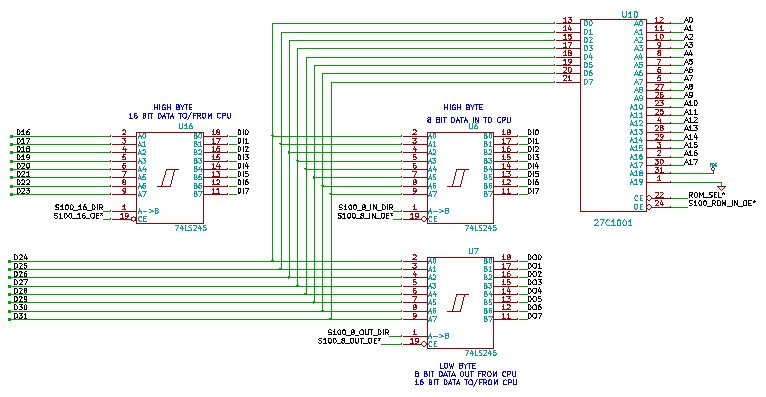

The board follows our 80386/80486 board format with the OTT connectors to allow it to address up to 4GB of RAM. The onboard EEPROM contains the 68030 monitor (see below). It runs at 9 MHz on the S100 bus in 8 & 16 bit modes and in 32 bit mode when addressing RAM on the OTT bus. The board works without any changes to our OTT 32/64MB RAM boards that we developed for the 80386/80486 CPUs. Also because of the much simpler RAM interface with this CPU it was not necessary to go to a 4 layer Full Size 68030 board -- as we had to do for the 80486 CPU board.

There is a jumper option (K7) to use a Flash RAM (29F040) instead of an EEPROM.

I will use the EEPROM here.

Almost all the above capabilities are programmed into the onboard Atmel 1508 CPLD. Let us step through the various functions/code this CPLD supplies.

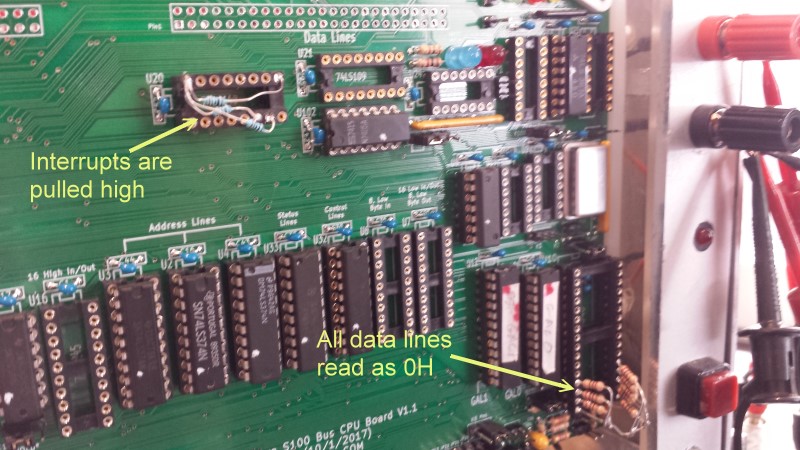

GAL0 Signals.

The current software assumes this 68030 board will act as an S100 bus slave. Later if needed, it can be modified/jumpered as being a bus master.

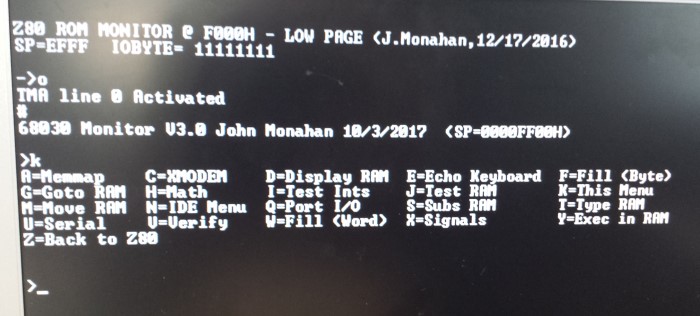

In hardware, one of the TMA lines (Jumper P13) goes low to start the S100 bus master/slave transfer process.

Just as for the 80486 board, sequentially XFERI & XFERII are then activated (and the S100 bus clock signal PHI, then originates from this board).

Pinnode = [reg2..0]; /* Need 3 D type Flip Flops */

Pinnode = BOARD_ACTIVE; /* BOARD_ACTIVE HIGH if 68030 has control of the bus, see below */

reg0.d = TMAx; /* TMAx goes low-> high */

reg0.ckmux = !PHI;

reg0.ar = !MASTER_RESET; /* Return to high on reset */

!HOLD = reg0; /* Lower S100 bus HOLD line */

!XFERI = reg0 & pHLDA; /* Activate the S100 bus Control lines, when pHLDA comes back */

reg1.d = reg0;

reg1.ck = pHLDA; /* S100 bus grants bus by raising pHLDA line */

reg1.ar = !reg0;

BOARD_ACTIVE = reg1; /* HIGH when bus control comes to this 68030 Board */

!XFERII = reg1; /* LOW to activate S100 bus Status, Data & Address lines */

reg2.d = reg1;

reg2.ckmux = !PHI;

reg2.ar = !reg1;

CPU_RESET = reg2; /* Activate the CPU, Raise it's reset pin */

This is the same approach we have used time and time again on all our S100 bus master/slave CPU boards. TMAx is the key signal that is either generated in "GAL0" (or generated on our