Distributed by:

# www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

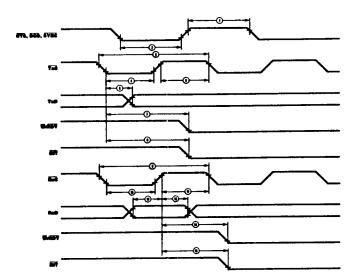

### AC CHARACTERISTICS TIMING (Continued)

Z8D is a registered trademark of Zilog, Inc.

Copyright 1986 by Zilog, Inc. All rights reserved. Specifications (parameters) on products delivered in the future ere subject to change without notice. All parameters ere tested, except those which are characterized or gueranteed by design.

Zilog, Inc. 1315 Dell Ave., Campbell, California 95008 Telephone (408)370-8000 TWX 910-338-7621

# Zilog

Z08470 Customer Procurement Spec (CPS)

#### GENERAL DESCRIPTION

The Z80 DART (Dual-Channel Asynchronous Receiver/ Transmitter) is a dual-channel multifunction peripheral component that satisfies a wide variety of asynchronous serial data communications requirements in microcomputer systems. The Z80 DART is used as a serial-to-parallel. parallel-to-serial converter/controller in asynchronous applications. In addition, the device also provides modern controls for both channels. In applications where modern controls are not needed, these lines can be used for general-purpose I/O.

40-Pin Dual-in-Line Package (DIP), Pin Assignments

#### DC CHARACTERISTICS

| Symbol         | Parameter                             |          | Marie . | Unit | Tool Condition               |

|----------------|---------------------------------------|----------|---------|------|------------------------------|

| Vac            | Clack Imput Law Voltage               | -0.3*    | +0.45*  | ٧    |                              |

| Vec            | Clock Input High Voltage              | VDC-0.6* | +5.54   | ٧    |                              |

| V <sub>R</sub> | Input Low Voltage                     | -0.3*    | +0.8*   | ٧    |                              |

| Var            | Input High Voltage                    | +2.0*    | + 5.5°  | ٧    |                              |

| Vos.           | Output Low Voltage                    |          | +0.44   | ٧    | los = 20mA                   |

| VOH            | Output High Voltage                   | +2.4*    |         | ٧    | IOH = -250 pA                |

| 4              | Input/3-State Output Lealings Current | - 10*    | + 10*   | pa A | 0.4 < Voy < 2.4V             |

| in.            | Fit Pin Leshage Current               | -40*     | + 10*   | ppA. | 0.4 < V <sub>IN</sub> < 2.4V |

| CC.            | Power Supply Current                  |          | . 100°  | mA   |                              |

T<sub>A</sub> = 0°C to 70°C, V<sub>CC</sub> = +5V, ±9%.

a Tested

b Gueranteed by Design

c Gueranteed by Characterization

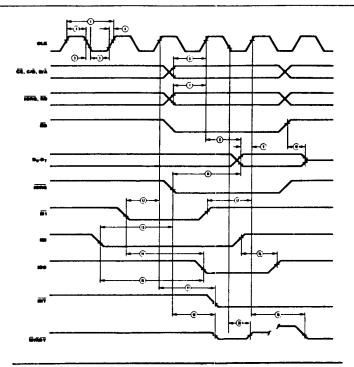

## AC CHARACTERISTICS\*

| Number | Symbol      | Parameter                                    | 280-4<br>Min | DART<br>Max | 280-6<br>Min | DART<br>Mess |

|--------|-------------|----------------------------------------------|--------------|-------------|--------------|--------------|

| 1      | ToC         | Clock Cycle Time                             | 250*         | 4000 °      | 165 *        | 4000         |

| 2      | TeCh        | Clock Width (High)                           | 106*         | 2000 °      | 70 *         | 2000         |

| 3      | TIC         | Clock Fell Time                              |              | 30 °        |              | 15           |

| 4      | TC          | Clock Rise Time                              |              | 30 *        |              | 15           |

| 5      | TwO         | Clock Width (Low)                            | 105 °        | 2000°       | 70°          | 2000         |

|        | TeAD(C)     | CE, C/D, B/Ā to Clock † Satup Time           | 145*         |             | 60*          |              |

| 7      | TeCS(C)     | IORO, RD to Clock 1 Setup Time               | 1150         |             | 60*          |              |

|        | TdC(DO)     | Clock 1 to Data Out Dalay                    |              | 220 °       |              | 150          |

|        | TsD(C)      | Date in to Clock & Setup (Write or M1 Cycle) | 50 *         |             | 30 *         |              |

| 10     | TdRD(DOz)   | RD 1 to Data Out Ploat Dalay                 |              | 110°        |              | 901          |

| 11     | TalO(DOI)   | IORO I to Date Out Datey (INTACK Cycle)      |              | 160°        |              | 1001         |

| 12     | TsM1(C)     | M1 to Clock 1 Setup Time                     | 90 *         |             | 75 ●         |              |

| 13     | TelEI(IO)   | IEI to IORQ 4 Setup Time (INTACK Cycle)      | 140 °        |             | 120 °        |              |

| 14     | TdM1(IEO)   | MT 4 to IEO 4 Daley (interrupt before M1)    |              | 190 °       |              | 160          |

| 15     | Talel(IEOr) | IEI 1 to IEO 1 Daley (after ED decode)       |              | 100 €       |              | 70           |

| 16     | Talei(IEOI) | ÆI ∔ to ÆO ∔ Dalay                           |              | 100 *       |              | 701          |

| 17     | TdC(INT)    | Clock 1 to INT # Daley                       |              | 200 *       |              | 150          |

| 18     | TalO(W/RWI) | IORG I or CE I to W/RDY IDelay (Mat Mode)    |              | 210¢        |              | 175          |

| 19     | TdC(W/RR)   | Clack 1 to W/RDY I Datey (Ready Mode)        |              | 120 *       |              | 100          |

| 20     | TdC(W/RWz)  | Clock I to W/RDY Float Datey (Wart Mode)     |              | 130°        |              | 110          |

\*Units in rendesconds (ris).

a Tested

b Guaranteed by Design

c Sucrenteed by Characterization

### AC CHARACTERISTICS (Commund)

| Number |              | Parameter                           | 18D-4 | DART       | 280-  | 6 DART     |        |

|--------|--------------|-------------------------------------|-------|------------|-------|------------|--------|

|        | Symbol       |                                     | Min   | Mex        | Min   | Mex        | Notes* |

| 1      | TwPh         | Pulse Width (High)                  | 200°  |            | 200¢  |            | 2      |

| 2      | TwPI         | Pulse Width (Low)                   | 200 € |            | 200¢  |            | 2      |

| 3      | TcTxC        | TrC Cycle Time                      | 400°  | c          | 330¢  | - c        | 2      |

| 4      | Twitci       | TrC Width (Low)                     | 180°  | -c         | 100 ¢ | <b>∞</b> ¢ | 2      |

| 5      | Tw/brCh      | TicC Width (High)                   | 180°  | æ¢.        | 100¢  | <b>-</b> c | 2      |

| 6      | Tellic(TxD)  | TirC ∔ to TirD Delay                |       | 300 *      |       | 220°       | 2      |

| 7      | Tdbc(W/RRI)  | SiC ∔ to W/RDY ∔ Delay (Ready Mode) | 5 0   | 9 c        | 5 c   | 9 c        | 1      |

| 8      | TdTkC(INT)   | ScC + to fNT + Delay                | 5 e   | <b>9</b> c | 50    | 90         | 1      |

|        | ToRxC        | RxC Cycle Time                      | 400 ¢ | ⇔ ¢        | 330¢  | - c        | 2      |

| 10     | TerRisCI     | FixC Width (Low)                    | 180°  | -c         | 100 ° | e c        | 2      |

| 11     | TwRxCh       | Ric Width (High)                    | 180°  | -c         | 100°  | es c       | 2      |

| 12     | TeRxD(RxC)   | RidD to RidC 1 Setup Time (x1 Mode) | 0¢    |            | 0 c   |            | 2      |

| 13     | ThRxD(RxC)   | RxD Hold Time (x1 Mode)             | 140¢  |            | 100 ° |            | 2      |

| 14     | TdRxC(W/RRI) | RxC 1 to W/RDY & Delay (Ready Mode) | 10°   | 13¢        | 10 °  | 13¢        | 1      |

| 15     | TdRxC(INT)   | RicC t to RT ∔ Delay                | 10°   | 13 C       | 10°   | 13¢        | 1      |

<sup>\*</sup> In all modes, the System Clock rate must be at least five times the maximum data rate RESET must be active a minimum of one complete clock cycle

1. Units equal to System Clock Periods.

2. Units in hancesconds (ns).

. Tested

b Guarenteed by Design c Guarenteed by Characterization